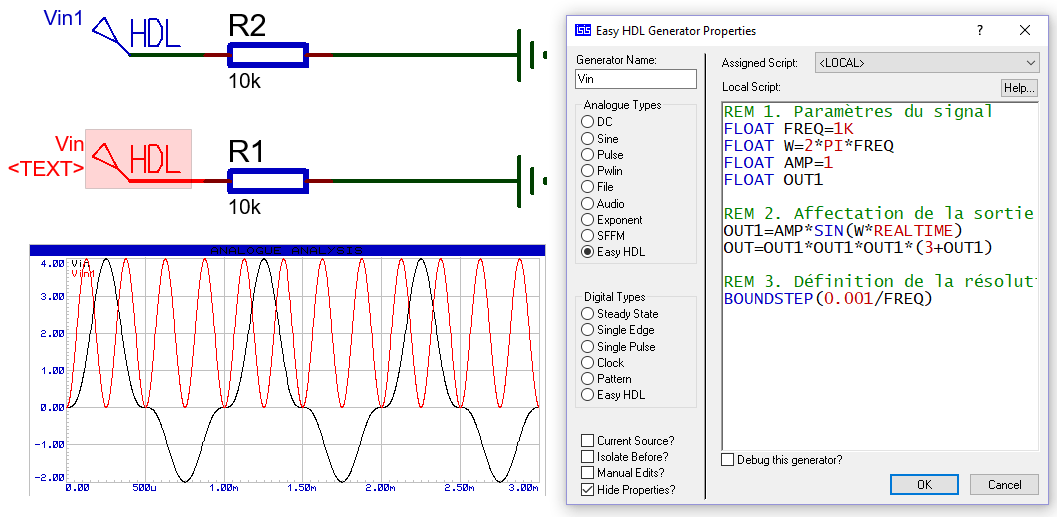

Objectifs

- Savoir activer l’outil Easy VHDL

- Savoir générer un signal sinusoïdal

- Savoir générer un signal composé

Fonctionnement

Le tutoriel est pour objectif d’apprendre comment synthétiser un signal complexe avec ISIS PROTEUS. L’outil Easy VHDL sera utilisé pour générer un signal sinusoïdal ou à base d’une expression complexe. Ci-dessous le script utilisé dans le tutoriel. En effet, la bibliothèque ISIS des signaux n’est pas toujours suffisante. Dés fois on a besoin des signaux spécifiques pour simuler notre montage. L’outil Easy VHDL vous permettra de générer le signal de votre choix. Voilà quelques exemples des fonctions usuelles supportées par l’outil Easy VHDL (SIN, COS, TAN, ROUND, EXP, etc.). Les Expressions : Multiplication, division, soustraction et addition.