Le kit d’évaluation Spartan®-6 FPGA SP605 offre commodément tous les

composants de base de Base de Xilinx ciblées, une plateforme de conception pour le développement diffusion, les communications sans fil, de l’automobile, et d’autres applications à très haute sensibilité, les applications qui nécessitent des capacités importantes de l’émetteur/récepteur dans un seul paquet.

Ce nouveau kit fournit une

l’intégration de matériels, logiciels, IP, et des designs de référence pré-vérifiés afin

de réduire le temps de développement et commencer dès la sortie de la boîte !

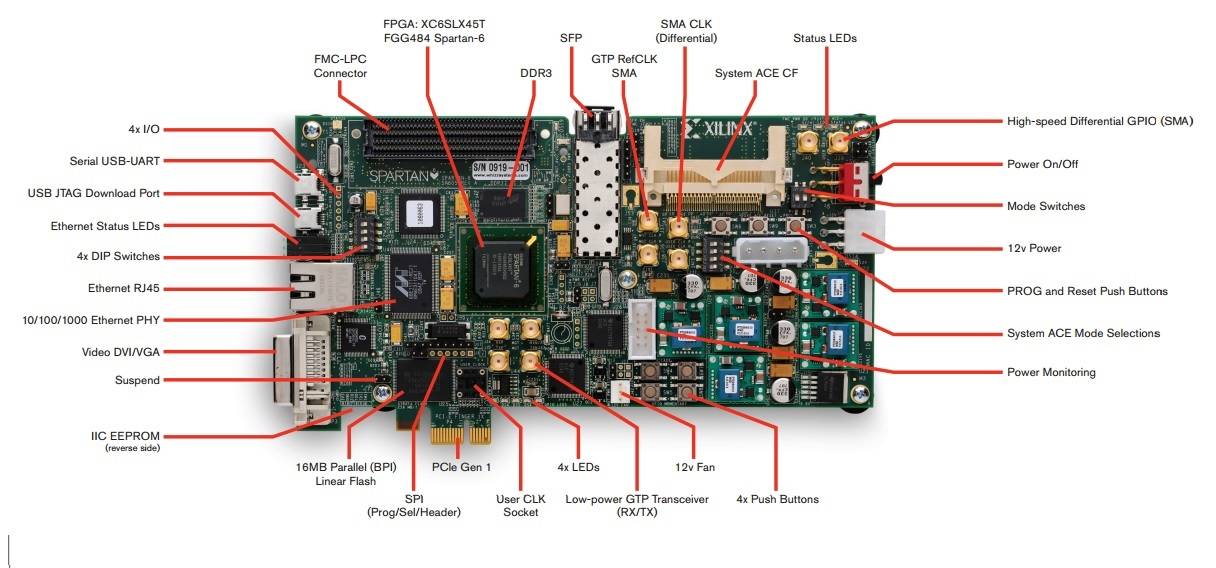

Caractéristiques de kit de développement SP605

- Le kit SP605 est basé sur l’FPGA XC6LX45T-FGG484-3 CES FPGA

- ISE® Design Suite Logic Edition: (device-locked) pour

- Spartan-6 LX45T FPGA

- Comprend ChipScope ™ Pro et Pro ChipScope

- Serial I/O Toolkit /

- Comprend PlanAhead ™ outil d’analyse et de conception

- Timing Driven Place et Route, SmartGuide ™ et SmartXplorer technologie

- Documentation

- Guide de configuration du matériel

- Guide de démarrage

- Hardware Guide de l’utilisateur

- Guide de conception de référence de l’utilisateur

- Schémas et fichiers PCB

- Alimentation universelle 12V

- Câbles: 2 USB, 1 Ethernet, 1 adaptateur DVI-VGA

- Conceptions de référence et démos

- Board Diagnostic Démo

- Système de base de conception de référence avec DSP48,

- Ethernet, mémoire, et l’intégration de série de l’émetteur-récepteur

- Multiboot de conception de référence, avec fail-safe

- configuration

- Controlleur de mémoire matériel

- Conceptions de référence, démos, la documentation et applications délivrées sur le lecteur flash USB pour obtenir démarrer rapidement

FPGA (Wikipedia)

Un circuit logique programmable, ou réseau logique programmable, est un circuit intégré logique qui peut être reprogrammé après sa fabrication. Notons qu’il serait impropre de parler de programmation au sens logiciel (contrairement à un microprocesseur, il n’exécute aucune ligne de code). Ici, mieux vaudrait parler de « reconfiguration » plutôt que de reprogrammation (on modifie des connexions ou le comportement du composant, on connecte des portes logiques entre elles, etc.). Le verbe programmer est toutefois le plus fréquent, mais au sens de personnaliser. Il s’agit bel et bien de réseaux logiques reconfigurables et modifiables.

Il est composé de nombreuses cellules logiques élémentaires et bascules logiques librement connectables (c’est justement la reconfiguration, ou programmation, du composant qui définit les connexions faites entre portes logiques).

Ce type de composant électronique est communément désigné par différents sigles anglais dont notamment :

- FPGA (field-programmable gate array, réseau de portes programmables in situ) ;

- PLD (programmable logic device, circuit logique programmable) ;

- EPLD (erasable programmable logic device, circuit logique programmable et effaçable) ;

- CPLD (complex programmable logic device, circuit logique programmable complexe) ;

- PAL (programmable array logic, réseau logique programmable) ;

- PLA (programmable logic array, réseau logique programmable)

La plupart des grands FPGA modernes sont fondés sur des cellules SRAM aussi bien pour le routage du circuit que pour les blocs logiques à interconnecter.

Un bloc logique est de manière générale constitué d’une table de correspondance (LUT ou Look-Up-Table) et d’une bascule (Flip-Flop en anglais). La LUT sert à implémenter des équations logiques ayant généralement 4 à 6 entrées et une sortie. Elle peut toutefois être considérée comme une petite mémoire, un multiplexeur ou un registre à décalage. Le registre permet de mémoriser un état (machine séquentielle) ou de synchroniser un signal (pipeline).

Les blocs logiques, présents en grand nombre sur la puce (de quelques milliers à quelques millions en 2007) sont connectés entre eux par une matrice de routage configurable. Ceci permet la reconfiguration à volonté du composant, mais occupe une place importante sur le silicium et justifie le coût élevé des composants FPGA. La topologie est dite « Manhattan », en référence aux rues à angle droit de ce quartier de New York.

Les densités actuelles ne permettent plus un routage manuel, c’est donc un outil de placement-routage automatique qui fait correspondre le schéma logique voulu par le concepteur et les ressources matérielles de la puce. Comme les temps de propagation dépendent de la longueur des liaisons entre cellules logiques, et que les algorithmes d’optimisation des placeurs-routeurs ne sont pas déterministes, les performances (fréquence max.) obtenues dans un FPGA sont variables d’un design à l’autre. L’utilisation des ressources est par contre très bonne, et des taux d’occupation des blocs logiques supérieures à 90 % sont possibles.

Comme la configuration (routage et LUTs) est faite par des points mémoire volatils, il est nécessaire de sauvegarder le design du FPGA dans une mémoire non volatile externe, généralement une mémoire Flash série, compatible « JTAG ». Certains fabricants se distinguent toutefois par l’utilisation de cellules EEPROM pour la configuration, éliminant le recours à une mémoire externe, ou par une configuration par anti-fusibles (la programmation par une tension élevée fait « claquer » un diélectrique, créant un contact). Cette dernière technologie n’est toutefois pas reconfigurable.

Quelques fonctionnalités particulières disponibles sur certains composants :

- Blocs de mémoire supplémentaires (hors des LUT), souvent double-port, parfois avec mécanisme de FIFO,

multiplieurs câblés (coûteux à implémenter en LUT), voire blocs multiplieur-accumulateur pour traitements DSP, - Cœur de microprocesseur enfoui (dit hard core) comme par exemple des architectures PowerPC ou ARM,

- Blocs PLL pour synthétiser ou resynchroniser les horloges,

- Reconfiguration partielle, même en cours de fonctionnement,

- Chiffrement des données de configuration,

- Sérialiseurs/désérialiseurs dans les entrées-sorties, permettant des liaisons série haut-débit,

- Impédance contrôlée numériquement dans les entrées-sorties, évitant de nombreux composants passifs sur la carte.

- Couche MAC Ethernet

- Couches matérielles

Retour aux kits de développement