Titre: Electronique Numérique Systèmes séquentiels

Auteurs: Etienne Messerli, Yves Meyer

Ecole: Ecole d’Ingénieurs du Canton de Vaud (EIVD)

Résumé: Nous avons étudié jusqu’ici des circuits logiques combinatoires dont les sorties, à un instant donné, ne dépendent que de l’état des valeurs présentes sur les entrées. Toute condition antérieure n’a aucun effet sur les valeurs actuelles des sorties, parce que les circuits combinatoires n’ont pas de mémoire.

Dans la majorité des systèmes numériques, on retrouve une combinaison de circuits combinatoires et de dispositifs à mémoire. La section combinatoire est alimentée par des signaux d’entrée externes et par les sorties des dispositifs à mémoire. Le circuit combinatoire agit sur ces entrées pour produire diverses sorties, certaines servant à déterminer les valeurs binaires stockées dans les éléments de mémoire. La sortie de certains de ces éléments de mémoire revient comme entrée des circuits logiques de la partie combinatoire. Ceci est une indication que les sorties externes d’un système numérique dépendent autant des entrées externes que des informations mémorisées dans d’autres sections. On appelle cela un système séquentiel.

Extrait du sommaire:

Chapitre 1 LES BASCULES 1

1-1 Définition du système séquentiel 2

1-2 Bascule R-S en portes NAND 2

1-3 Bascule R-S en portes NOR 3

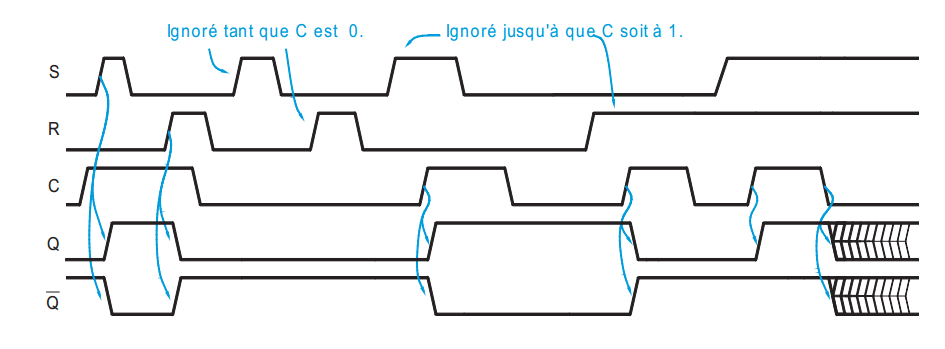

1-4 Bascule R-S avec enable 4

1-5 L’élément mémoire D (D Latch) 5

1-6 La bascule maître-esclave 6

1-7 La bascule bistable déclenchable sur un flanc « edge-triggered » 8

1-8 Signal d’horloge et bascules synchrones 9

1-9 FLIP-FLOP D 10

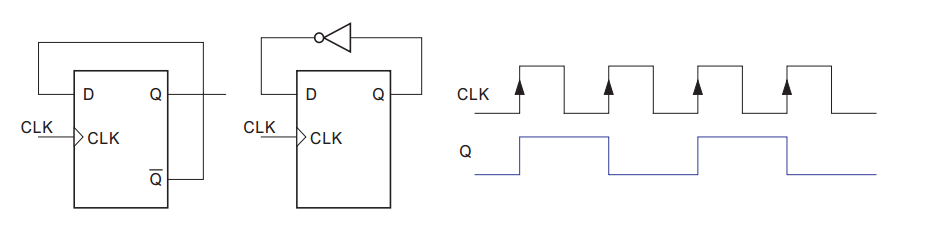

1-10 BASCULE T (Toggle flip flop) 10

1-11 Entrées asynchrones 10

1-111Désignation des entrées asynchrones 11

1-12 Considérations sur la synchronisation des bascules 11

1-121Temps de stabilisation (setup time) et temps de maintien (hold time) 12

1-122Temps de propagation 12

1-13 Description d’une bascule D avec reset asynchrone en VHDL 13

1-14 Synchronisation des entrées externes asynchrones 14

Chapitre 2 Synchronisation et détection des flancs d’un signal externe asynchrone 17

Chapitre 3 Les Registres 19

3-1 Structures de base des registres 19

3-2 Registre Tampon (registre parallèle) 20

3-21Description VHDL d’un registre tampon 21

3-3 Registre mémoire21

3-31Bus de données bidirectionnel21

3-32Structure d’un registre mémoire22

3-33Description VHDL23

3-4 Les registres à décalage24

3-41Registre serial IN serial OUT25

Description VHDL25

3-42Registre serial IN parallel OUT26

Description VHDL27

3-43Registre parallel IN serial OUT27

Description VHDL28

3-44Registre parallel IN parallel OUT29

Description VHDL29

Chapitre 4 Les machines d’états synchrones 31

4-1 Structure interne d’une machine d’états33

4-2 Le graphe des états (diagramme de transition)33

4-21Table de vérité des sorties en fonction de l’état35

4-3 Du graphe des états à la description VHDL35

4-31Codage des états35

4-32Machines de Moore36

4-33Machines de Mealy37

4-34Machines de Mealy à sorties resynchronisées37

Chapitre 5 Les Compteurs 39

5-1 Les Compteurs Asynchrones39

5-11Modulo40

5-12Division de la fréquence40

5-13RETARD DE PROPAGATION DANS LES COMPTEURS ASYNCHRONES

5-14Compteurs asynchrones modulo < 2N41

5-2 COMPTEURS SYNCHRONES (PARALLÈLES)42

5-3 COMPTEURS PRÉRÉGLABLES44

5-4 Description d’un compteur synchrone en VHDL44

Télécharger le fichier PDF: Electronique Numérique Systèmes séquentiels