# Première partie Cours d'électronique

## Chapitre 1

# Simulation des circuits électroniques : SPICE

#### 1 - Introduction

La simulation par ordinateur constitue une aide puissante pendant la phase de conception ou pour l'analyse des circuits et des composants semi-conducteurs. Ce chapitre est essentiellement consacré à la simulation des circuits analogiques. Cette technique pourrait bien entendu être appliquée aux circuits numériques (qui sont en fait composés de circuits analogiques) mais la principale limitation provient de la taille des circuits car les méthodes présentées ici fourniraient une analyse trop détaillée du circuit étudié qui coûterait beaucoup trop cher en termes de ressources (mémoire et temps de calcul) pour analyser de manière analogique un système numérique de grande taille.

Le programme de simulation analogique le plus répandu et le plus utilisé actuellement est « SPICE » (Simulation Program with Integrated Circuit Emphasis : Programme de Simulation Orienté vers les Circuits Intégrés). Ce programme a été développé au départ à l'Université de Berkeley en Californie par Laurence Nagel en 1975 mais les recherches dans le domaine de la simulation des circuits se poursuivent encore actuellement dans un grand nombre d'universités ou d'entreprises. Des versions gratuites ou commerciales de SPICE ou de programmes similaires sont actuellement disponibles sur un grand nombre de platesformes qui vont du petit ordinateur personnel aux grosses machines centrales en passant par les stations de travail. On peut citer quelques versions telles que SPICE2 ou SPICE3 (Berkeley), PSpice (MicroSim/Orcad¹), Hspice (Meta Software), ISpice (Intusoft), Spectre (Cadence), Saber (Analogy), Smash (Dolphin Intégration)...

Il est possible de simuler pratiquement n'importe quel circuit avec un programme tel que SPICE. Ce programme comporte des modèles constitutifs pour les résistances, les condensateurs, les inductances, les sources de courant et de tension indépendantes ou commandées, les diodes, les transistors MOS, FET, bipolaires, les lignes de transmission, les transformateurs, certaines versions comportent même des transformateurs à noyau saturé. Les versions commerciales comportent en plus des bibliothèques de composants standard dont les paramètres ont été ajustés pour représenter les spécifications typiques. Ces bibliothèques comportent des éléments tels que : transistors discrets, amplificateurs

<sup>&</sup>lt;sup>1</sup>À présent Cadence Design System distribué en France par ALS Design.

opérationnels, boucles à verrouillage de phase, régulateurs de tension, circuits intégrés logiques et transformateurs à noyau saturé.

La simulation par ordinateur est maintenant considérée comme une phase essentielle dans la conception des circuits intégrés car sans elle le nombre de prototypes d'essai nécessaires pour produire un circuit intégré opérationnel augmenterait considérablement le coût du circuit. La simulation présente également d'autres avantages :

- La possibilité de mesurer des tensions et des courants « inaccessibles ». Le modèle mathématique permet en effet d'accéder à tous les courants et tensions du circuit. Il n'y a pas de risque de rencontrer un problème de charge en plaçant un voltmètre ou un oscilloscope au milieu d'un circuit ou de placer une sonde dans une puce microscopique, de même il est possible de visualiser un court régime transitoire qui serait dans la pratique très difficile à mesurer.

- Le simulateur dispose de « composants » mathématiques idéaux. Créer une source de tension ou de courant idéale avec un simulateur est une opération triviale impossible à réaliser en pratique, de plus toutes les valeurs des composants sont exactes et il n'existe pas d'éléments parasites.

- Il est très facile de changer la valeur d'un composant ou la configuration du circuit sans être obligé de dessouder des connexions ou de redessiner un masque de circuit intégré.

La simulation par ordinateur peut cependant avoir un certain nombre d'inconvénients :

- Les circuits réels sont en fait des circuits à constantes réparties et non les « modèles à constantes localisées » supposés par le simulateur. En effet, les circuits réels comportent des éléments parasites résistifs, capacitifs et inductifs en plus des composants effectifs. Dans les circuits très rapides ces éléments parasites sont les principales causes de limitation des performances et doivent être minutieusement modélisés.

- Les modèles numériques prédéfinis pour certains types de composants ou de phénomènes électriques n'ont pas encore été développés, l'utilisateur du programme peut alors être amené à créer ses propres modèles à partir des modèles disponibles dans le simulateur (par exemple un thyristor peut être créé à partir d'un transistor NPN et d'un transistor PNP).

- Les méthodes numériques utilisées peuvent imposer des contraintes sur la forme des équations représentatives des modèles utilisés<sup>2</sup>.

#### 2 - SPICE et ses versions

#### 2.1 - Origine

Parmi les très nombreuses versions disponibles, deux versions de SPICE utilisables avec un PC sous Windows<sup>TM</sup> sont disponibles sur les ordinateurs de l'école, toutes deux sont des adaptations de programmes originaux développés à l'Université de Californie à Berkeley (UCB). La première, commerciale, appelée *PSpice*<sup>3</sup> est issue de la version SPICE2G6 de

<sup>&</sup>lt;sup>2</sup>Ce paragraphe d'introduction est inspirée de la Section 13.1 « Analog Circuit Simulation » du *Electrical Engineering Handbook*, Richard C. Dorf Ed. CRC Press LLC, J. Gregory Rollins (1997).

<sup>&</sup>lt;sup>3</sup>Distribution en France : ALS Design, 160bis Rue de Paris – 92645 Boulogne Cedex. http://www.alsdesign.fr. Voir aussi le site : http://www.electronics-lab.com/downloads/schematic/013/.

l'UCB; l'autre « freeware » libre d'utilisation et de reproduction, appelée WinSpice<sup>4</sup> est une adaptation de SPICE3F5 de l'UCB.

À quelques nuances près, la description des composants et les analyses réalisables avec ces deux simulateurs sont identiques, les différences tiennent principalement à la philosophie d'utilisation des programmes d'origine :

- SPICE2, le plus ancien, fonctionne uniquement en mode « batch » (traitement par lot) le circuit et les commandes sont décrites dans un fichier d'entrée et les résultats produits par le programme sont enregistrés dans un fichier de sortie. Cette philosophie a été conservée dans le mode de fonctionnement de *PSpice*.

- SPICE3 est en fait une version « interactive » de SPICE2, le circuit, toujours décrit par un fichier d'entrée, est chargé dans une fenêtre de commande où sont exécutées les instructions d'analyse et où peuvent être consultés les résultats. Pour des raisons de compatibilité avec SPICE2, les commandes peuvent également être décrites dans le fichier d'entrée.

Les avantages et les inconvénients de ces deux versions tiennent plus à leur mode de diffusion qu'à leur principe de fonctionnement :

- PSpice est un produit professionnel commercial très répandu actuellement, à ce titre chaque licence doit être achetée (il existe toutefois une version d'évaluation gratuite mais « bridée »). En contrepartie ce programme robuste et convivial dispose de bibliothèques de composants très complètes, d'une saisie de schéma graphique, d'un post-processeur graphique ainsi que d'autres fonctionnalités, d'une documentation abondante, d'une maintenance de produit et d'une assistance technique suivies.

- WinSpice est un programme gratuit (jusqu'à aujourd'hui), libre d'utilisation et de reproduction et n'est limité que par les capacités de la machine utilisée (pas de limitation du nombre de composants ou du nombre de nœuds). Ce programme développé bénévolement est mis sans engagement de responsabilité à la disposition de la communauté des électroniciens, il ne dispose pas encore de saisie de schéma; la sortie graphique, les bibliothèques et la documentation restent relativement limitées. Ces inconvénients sont cependant atténués par l'existence d'une communauté active d'utilisateurs qui échangent volontiers leurs expériences et par l'existence de nombreuses bibliothèques gratuites mises à disposition par les fabricants de composants et de circuits.

Les principales commandes de SPICE seront illustrées à l'aide de *PSpice*, le lecteur intéressé pourra traiter les mêmes exemples avec *WinSpice*.

#### 2.2 - PSpice

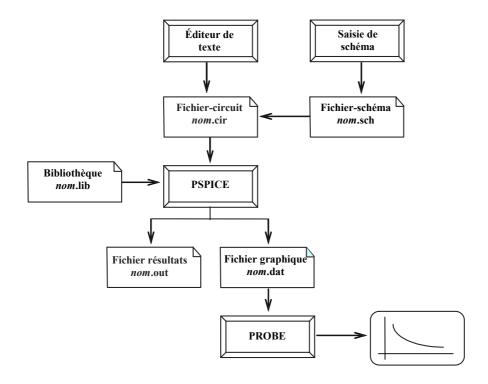

Le synoptique d'utilisation de PSpice est résumé sur la figure 1. La simulation d'un circuit électrique ou électronique commence toujours par la description du circuit. Celle-ci peut être réalisée à l'aide d'un éditeur de texte ou d'un programme de saisie graphique de schéma (préprocesseur) qui convertira le schéma en fichier texte. Ce fichier appelé « fichier-circuit » contient également les instructions concernant les analyses à réaliser. Pour procéder à la simulation, il faut exécuter le programme PSpice en précisant le nom du fichier-circuit : nom.cir où « nom » est un nom de fichier donné par l'utilisateur et l'extension « .cir » est réservée. Après exécution du programme, les résultats de la simulation sont enregistrés

<sup>&</sup>lt;sup>4</sup>Mike Smith, 35 Rampton End – Willingham – Cambridge – Cambridgeshire – England CB4 5JB. mike@winspice.com. http://www.winspice.com.

Fig. 1 - Synoptique d'utilisation de PSpice.

dans le fichier texte de sortie nom.out et, si la demande en a été faite, les résultats sont également enregistrés dans le fichier binaire nom.dat pour pouvoir être traités par le postprocesseur graphique Probe.

### 3 – Exemple d'introduction

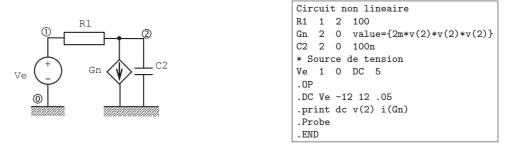

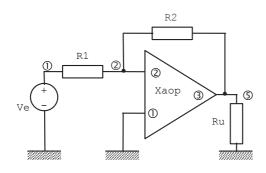

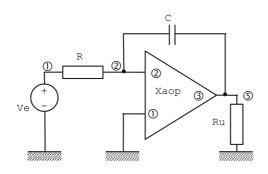

#### 3.1 – Création du fichier-circuit

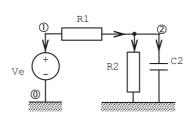

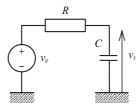

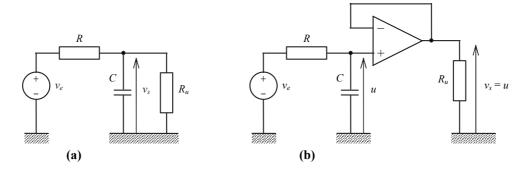

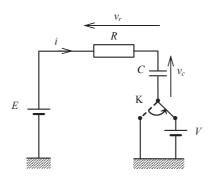

Pour illustrer l'utilisation de *PSpice*, prenons le cas du simple circuit RC représenté sur la figure 2. La première opération consiste à créer à l'aide d'un éditeur de texte (*PSpice* dispose d'un éditeur intégré pour la rédaction des fichiers textes) le fichier-circuit qui sera appelé dans ce cas particulier «rc.cir» décrivant la nature, la valeur ou les caractéristiques des sources et des composants utilisés ainsi que la connectivité du circuit à l'aide des instructions et en respectant la syntaxe SPICE. Le fichier contient également les commandes nécessaires pour effectuer les analyses, fixer des conditions initiales, structurer le fichier ou éditer les résultats. La figure 2 montre le fichier-circuit constitué par des lignes de description de composant qui commencent toujours par un caractère alphabétique et par des lignes de commande qui commencent toujours par un point.

Chaque ligne constitue une instruction complète, la première ligne est une ligne de titre, le texte de cette ligne est sans importance mais elle est obligatoire (si l'on commençait le fichier avec la première instruction, elle serait ignorée). La dernière ligne de commande .END, également obligatoire, marque la fin du circuit. À part la première et la dernière ligne dont l'emplacement est imposé par la syntaxe, les autres lignes d'instructions peuvent

```

Simple Pont RC

* Fichier rc.cir

R.1

1K

2

R.2

0

1K

100n

* Source de tension

DC

1

AC

SIN(0 100m

10k)

.DC Ve -10 10 .02

.AC dec 10 1 10meg

.TRAN 1u 300u 0 1u

.Probe

. FND

```

Fig. 2 - Simple circuit montrant le sens conventionnel des courants et fichier-circuit rc.cir...

être placées dans n'importe quel ordre et SPICE ne fait pas de différence entre minuscules et majuscules. La cinquième ligne qui commence par un astérisque est une ligne de commentaire : toute ligne commençant par \* est ignorée par l'interpréteur de commandes.

#### 3.2 – Instructions de description des composants

Une ligne de description de composant est constituée de différents champs (mots-clés, nœuds, valeur numérique, nom de modèle...) séparés par un ou plusieurs caractères séparateurs (espace, tabulation, signe =, virgule, parenthèse). La ligne commence par un mot-clé dont la première lettre identifie la nature du composant selon une syntaxe proche des usages en électronique (R pour résistance, C pour condensateur, L pour self, etc.), comme le montre le tableau II page 30. La première lettre peut être suivie d'un ou plusieurs caractères alphanumériques permettant de distinguer les composants, il ne doit pas y avoir de séparateur à l'intérieur d'un mot-clé. Le nom du composant est suivi de la liste des nœuds auxquels le composant est connecté. Chaque nœud est identifié de manière unique par un nombre ou plus généralement par une chaîne de caractères ne contenant pas de séparateur. La ligne se termine par la valeur du composant ou par la description de ses caractéristiques. Lorsqu'une instruction est trop longue elle peut être poursuivie sur une ou plusieurs lignes consécutives, le premier caractère de ces lignes-suite doit être le signe « + », voir figure 2. Sur la figure 2, la résistance R1 est connectée entre les nœuds 1 et 2 et vaut 1 k $\Omega$ , la résistance R2 de 1 k $\Omega$ , est connectée en parallèle sur la capacité C2 de 100 nF entre le nœud 2 et la masse identifiée par le nœud « 0 » réservé pour cet usage. La présence du nœud de masse 0 est obligatoire dans tous les fichiers-circuits, c'est par rapport à ce nœud de référence que sont calculées toutes les tensions du circuit<sup>5</sup>. Enfin le circuit est alimenté entre le nœud 1 et la masse par une source de tension Ve dont la composante continue (DC) vaut 1 V, l'amplitude de la composante alternative (AC) vaut 1 V et la composante temporelle (SIN) est une sinusoïde d'amplitude 100 mV et de fréquence 10 kHz. Noter que les valeurs numériques peuvent être écrites avec un suffixe multiplicatif, la liste de ces suffixes est résumée sur le tableau I page 13, il ne doit pas y avoir de séparateur entre le nombre et le suffixe multiplicatif.

L'ordre des nœuds définit la polarité du composant. Dans un dipôle, le courant est positif s'il entre par le 1<sup>er</sup> nœud et sort par le second quel que soit le composant : générateur ou récepteur, ainsi si l'on demande à SPICE de calculer le courant continu fourni par la source

$<sup>^5</sup>$ Avec PSpice, le mot-clé réservé GND (ground) peut également être utilisé à la place de « 0 ».

Ve, il indiquera une valeur négative car le courant est compté positivement s'il traverse le composant du 1<sup>er</sup> nœud (nœud 1) vers le second (nœud 0) alors que le sens réel est opposé (Fig. 2).

#### 3.3 – Instructions de commandes

Les trois lignes de commande qui suivent la description des composants instruisent le simulateur de réaliser les trois principaux types d'analyse que l'on peut effectuer sur un circuit et sur lesquels nous reviendrons :

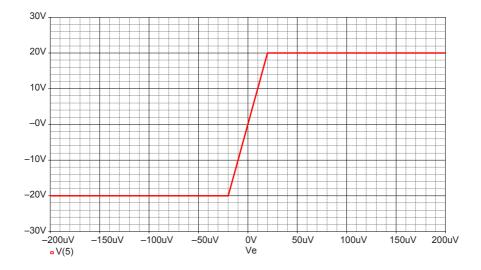

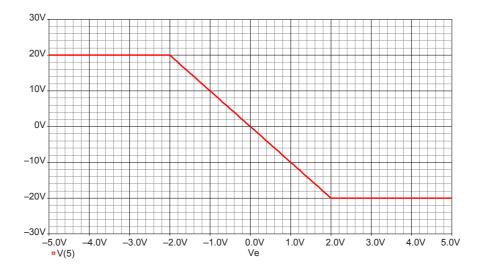

- .DC: analyse en courant continu, seules les sources de tension et de courant continus sont prises en compte, les condensateurs sont considérés comme des circuits ouverts, les inductances comme des courts-circuits. Cette analyse tient compte des éventuelles non-linéarités des caractéristiques des composants. Bien que la valeur de la source varie, cette variation doit être considérée comme une succession d'états permanents indépendants du temps. Dans l'exemple traité, la tension Ve varie de 10 V à + 10 V par pas de 20 mV.

- .AC: analyse dynamique en petits signaux, elle commence toujours par le calcul du point de polarisation en courant continu suivi de la linéarisation des caractéristiques des composants non linéaires (lorsqu'il y en a) pour conduire au schéma équivalent linéaire au voisinage du point de polarisation. Cette linéarisation n'a de sens que si l'amplitude des signaux est suffisamment faible pour que les caractéristiques non linéaires des composants puissent être remplacées par un segment de droite (développement limité au premier ordre). Les sources de tension ou de courant comportant le paramètre AC (Fig. 2) sont alors des sources sinusoïdales de fréquence variable. La gamme de fréquence à analyser est indiquée dans les paramètres de la commande .AC, ici la fréquence varie de 1 Hz à 10 MHz en échelle logarithmique à raison de 10 points par décade. Noter bien que du fait que l'analyse est réalisée sur un schéma linéaire, l'amplitude de la source AC n'est en réalité qu'un facteur d'échelle, si l'amplitude est multipliée par k toutes les tensions et tous les courants dans le circuit seront multipliés par le même facteur k c'est pourquoi on lui attribue très souvent la valeur 1 qui permet d'obtenir plus simplement les fonctions de transfert.

- .TRAN : analyse temporelle (transient), c'est l'analyse la plus complète que l'on puisse réaliser puisqu'elle détermine le comportement en fonction du temps d'un circuit généralement non linéaire. Elle commence par la détermination de l'état de polarisation initial qui servira de condition initiale pour le calcul temporel et qui commence donc nécessairement à l'instant t=0. Les signaux obtenus au cours de cette analyse sont ceux que l'on obtiendrait sur l'écran d'un oscilloscope branché sur un circuit réel. Les paramètres de la commande .TRAN précisent la façon dont doit s'effectuer la simulation, ici le pas d'édition des résultats est de 1  $\mu$ s, la durée totale de simulation est de 300  $\mu$ s, les résultats doivent être édités depuis l'instant t=0 et le pas maximal de calcul autorisé est de 1  $\mu$ s (par défaut, PSpice utilise un algorithme adaptatif pour accélérer les calculs).

La commande .Probe demande à PSpice de créer le fichier rc.dat qui sera utilisé par le post-processeur graphique Probe pour visualiser les résultats.

#### 3.4 – Exécution du programme, fichier de sortie

```

**** 07/28/101 19:27:03 ******* NT Evaluation PSpice (July 1997) ********

Simple Pont RC

CIRCUIT DESCRIPTION

************************

R1 1 2 1K

R2 2 0 1K

C2 2 0 100n

* Source de tension

Ve 1 0 DC 1

AC 1

SIN(0 100m 10k)

.OP

.DC Ve -10 10 .02

.AC dec 10 1 10meg

.TRAN 1u 300u 0 1u

.Probe

.END

**** 07/28/101 19:27:03 ***** NT Evaluation PSpice (July 1997) ****

Simple Pont RC

TEMPERATURE = 27.000 DEG C

**** SMALL SIGNAL BIAS SOLUTION

***********************************

NODE VOLTAGE

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

1.0000 ( 2)

( 1)

.5000

VOLTAGE SOURCE CURRENTS

NAME

CURRENT

-5.000E-04

TOTAL POWER DISSIPATION 5.00E-04 WATTS

**** 07/28/101 19:27:03 ***** NT Evaluation PSpice (July 1997) *********

Simple Pont RC

INITIAL TRANSIENT SOLUTION

TEMPERATURE = 27.000 DEG C

***********

*************

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 0.0000 ( 2) 0.0000

VOLTAGE SOURCE CURRENTS

NAME

CURRENT

0.000E+00

TOTAL POWER DISSIPATION 0.00E+00 WATTS

JOB CONCLUDED

TOTAL JOB TIME

```

Fig. 3 – Fichier de sortie pour le circuit RC de la figure 2.

Il existe plusieurs méthodes pour lancer l'exécution du programme, la plus simple consiste à exécuter le programme PSpiceAD, indiquer le chemin d'accès au fichier-circuit par le menu « File>Open » et lancer la simulation par la commande « Simulation>Run ». S'il n'y a pas d'erreur dans le fichier, les analyses indiquées sont réalisées et une fenêtre indique que la simulation a été exécutée avec succès. Il est alors possible de consulter les résultats en examinant le fichier de sortie « rc.out » dont un extrait est représenté sur la figure 3. Pour lire ce fichier on peut utiliser un éditeur de texte tel que le bloc-notes ou l'éditeur PSpice. La manière la plus simple de procéder est d'appeler le fichier de sortie dans la fenêtre PSpiceAD par le menu «  $View>Output\ File$  » (Fig. 3).

Par défaut le fichier d'entrée est restitué dans le fichier de sortie. La suite du fichier comporte deux rubriques, la première appelée SMALL SIGNAL BIAS SOLUTION indique l'état de polarisation du circuit en vue d'une analyse petits signaux (commande .AC) : les **tensions continues** en chaque nœud du circuit sont indiquées ainsi que les **courants continus**

débités par les sources de tension et la puissance totale fournie par les sources de tension. Dans cet exemple, comme on pouvait s'y attendre, la tension continue au nœud 1 vaut 1 V et celle du nœud 2 vaut 0,5 V. Le courant continu débité par la source Ve est de -0,5 mA et la puissance totale fournie est de 0,5 mW. La seconde rubrique intitulée INITIAL TRANSIENT SOLUTION résulte de la commande .TRAN (calcul temporel) elle donne l'état de polarisation du circuit à l'instant initial lorsque la source de tension continue est remplacée par la source de tension sinusoïdale. À l'instant initial toutes les tensions et tous les courants sont nuls dans ce cas. Les informations contenues dans ce fichier de sortie peuvent paraître assez pauvres dans cet exemple simple mais elles peuvent aussi être extrêmement détaillées et précieuses pour l'étude du comportement d'un circuit, de plus si une erreur se produit au cours de l'interprétation ou de l'exécution du fichier-circuit, sa description figure dans le fichier de sortie. Il est donc fortement conseillé de le consulter.

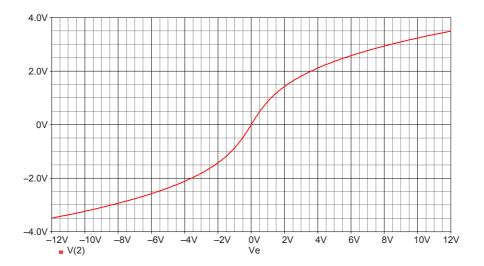

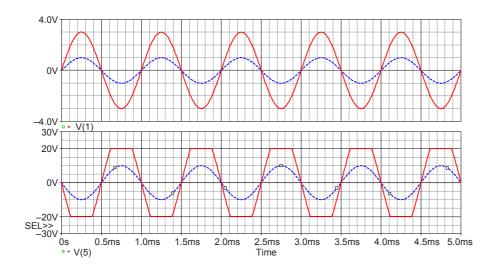

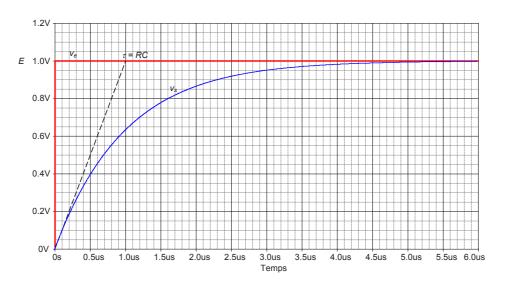

#### 3.5 - Visualisation graphique des résultats

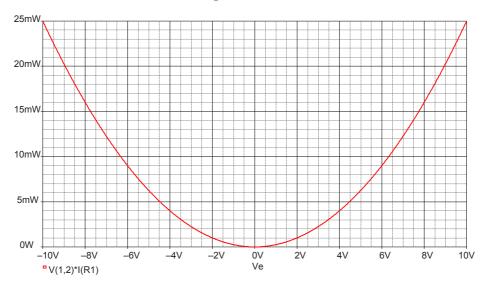

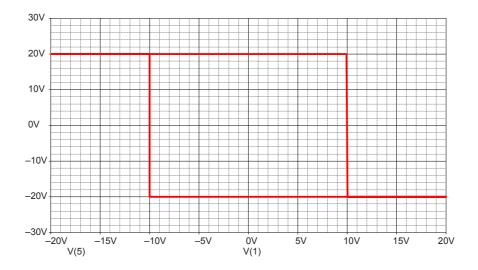

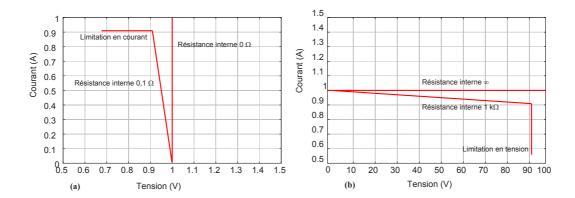

La manière la plus simple de visualiser le résultat des différentes analyses à l'aide du post-processeur Probe consiste à l'appeler dans la fenêtre PSpiceAD par le menu « View>Simulation Results » (la plupart du temps, la fenêtre graphique Probe s'ouvre automatiquement après la simulation). Lorsque plusieurs analyses ont été réalisées dans le même fichier, comme ici, Probe demande quelle analyse il doit représenter (AC, DC, Transient). Si l'option DC a été choisie, une fenêtre graphique s'ouvre (Fig. 4) où l'on peut voir que par défaut l'axe des abscisses porte le nom de la variable Ve et qu'il est gradué entre les valeurs limites indiquées dans la commande .DC. L'utilisation de Probe est assez intuitive et sera détaillée en TD et en TP. La figure 4 montre comment représenter par exemple la puissance dissipée dans la résistance R2 en fonction de la tension d'alimentation, noter que l'axe des ordonnées est dans ce cas gradué dans l'unité convenable.

Fig. 4 – Fenêtre graphique «Probe» pour l'analyse DC.

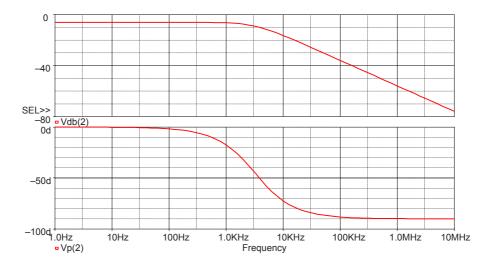

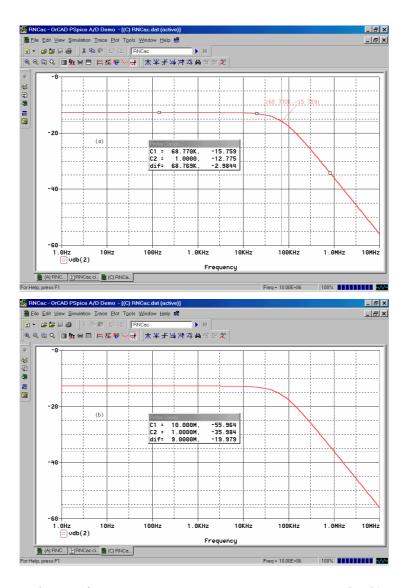

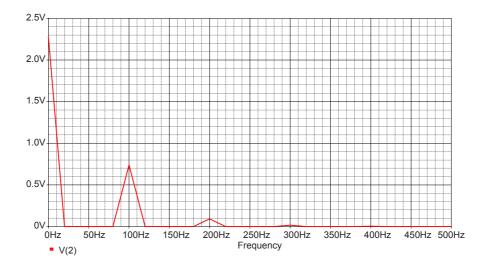

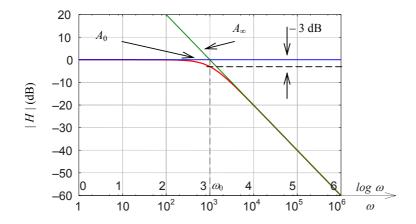

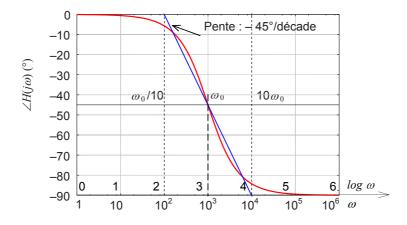

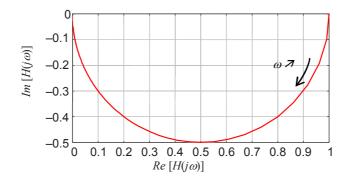

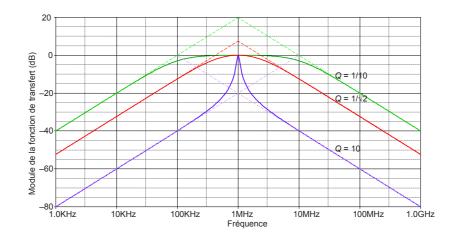

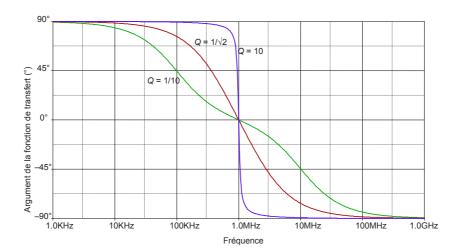

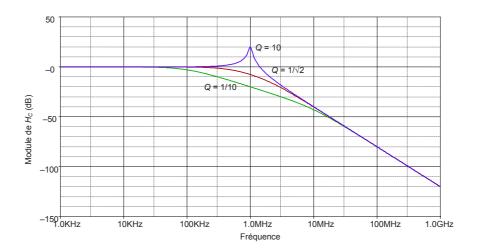

Si l'option AC est choisie au moment de l'appel de *Probe*, la fenêtre graphique représentée sur la figure 5 indique en abscisse l'axe des fréquences gradué en échelle logarithmique entre les limites indiquées dans la commande .AC. Il est alors possible de représenter par

exemple la fonction de transfert du filtre dans le plan de Bode en traçant l'amplitude en dB et la phase en degrés de la tension au nœud 2 qui s'écrivent respectivement vdb(2) et vp(2) (cf. tableau VI page 33 et tableau VII page 34). Noter que pour obtenir la fonction de transfert il n'est pas nécessaire d'effectuer le rapport avec la tension d'entrée puisque celle-ci a une amplitude unité (Fig. 2).

Fig. 5 – Fenêtre graphique « Probe » pour l'analyse AC.

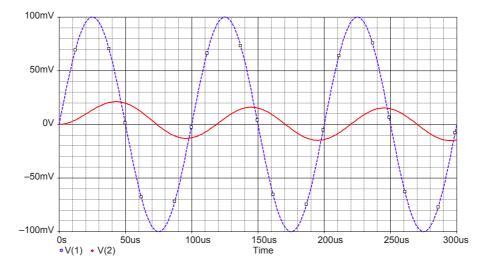

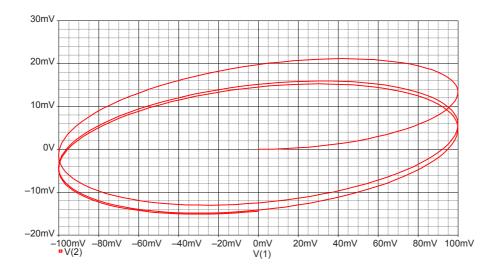

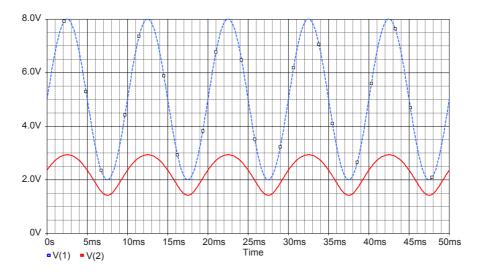

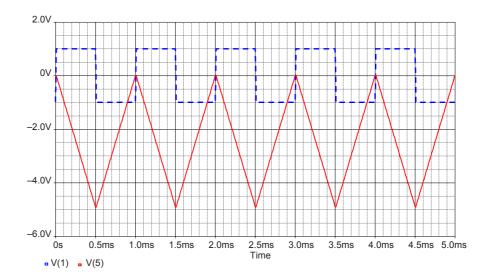

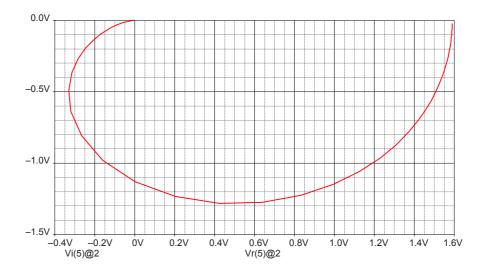

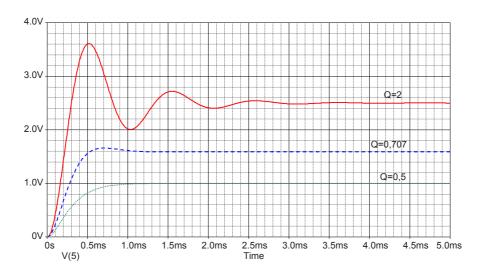

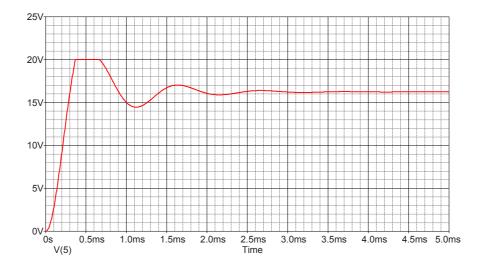

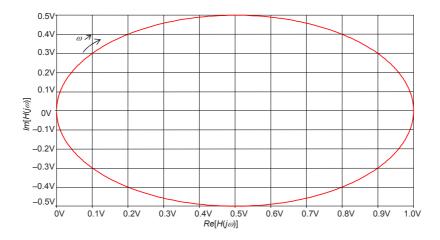

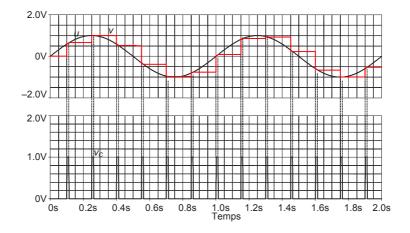

Enfin si *Probe* est appelé avec l'option TRAN, la fenêtre graphique indique automatiquement l'axe des temps gradué dans les limites indiquées par la commande .TRAN. Il est alors possible de visualiser la forme des signaux aux différents points du circuit comme le montre la figure 6. Bien que l'axe des abscisses soit par défaut gradué en fonction de la variable principale de l'analyse choisie, il est possible de changer l'échelle ou la nature de la variable utilisée comme le montre la figure 7 qui représente par exemple les tensions d'entrée et de sortie en mode de Lissajous.

Fig. 6 – Fenêtre graphique « Probe » pour l'analyse TRAN.

Fig. 7 - Changement d'abscisse dans « Probe ».

#### 4 – Constantes, composants et commandes SPICE

Ce paragraphe ne prétend pas constituer un document de référence pour l'utilisation de SPICE mais seulement de donner à l'utilisateur quelques notions de base nécessaires pour une utilisation courante. La documentation complète qui accompagne les différentes versions de SPICE devra être consultée pour plus de détails sur la syntaxe et l'exécution des commandes ou sur la présentation et l'exploitation des résultats d'analyses. En ce qui concerne *PSpice*, une documentation très complète est accessible en ligne.

#### 4.1 – Constantes numériques

En plus du format utilisant les suffixes multiplicatifs résumés dans le tableau I page 13, les constantes numériques peuvent être écrites sous la plupart des formats reconnus par les applications informatiques, ainsi : 120 120.00 1.2e2 1.2E2 0.12k 0.12kHz sont tous des formats acceptables. Si une chaîne de caractères suit un suffixe multiplicatif elle est ignorée (dans le dernier exemple Hz qui suit k est ignoré). De même si une chaîne de caractères suivant immédiatement un nombre n'est pas reconnue comme un suffixe multiplicatif elle est ignorée : 100 100V 100volts 100Hz représentent tous la même quantité (les unités sont ignorées).

Exemples: R1 1 2 1K C2 2 0 100nF McanalP 2 1 3 3 MOSP L=10u W=10u

Pièges à éviter :  $1 \text{megaHz} = 10^6 \text{ (mais } 1 \text{MHz} = 10^{-3}), 1 \text{pF} = 10^{-12} \text{ (mais } 1 \text{F} = 10^{-15}).$

#### 4.2 - Composants analogiques

Les composants analogiques sont identifiés par la première lettre du mot-clé comme indiqué dans le tableau II page 30.

Exemples: | Ve 1 0 DC 1 | Q1 3 10 5 ca3086

| Suffixe | Signification | Valeur          |

|---------|---------------|-----------------|

| F       | femto         | $10^{-15}$      |

| P       | pico          | $10^{-12}$      |

| N       | nano          | $10^{-9}$       |

| U       | micro         | $10^{-6}$       |

| MIL     | milli-inch    | $25.4  10^{-6}$ |

| M       | milli         | $10^{-3}$       |

| K       | kilo          | $10^{3}$        |

| MEG     | mega          | $10^{6}$        |

| G       | giga          | $10^{9}$        |

**Tableau** I – Suffixes multiplicatifs reconnus par SPICE.

Noter sur cet exemple que dans le cas des composants actifs (diodes, BJT, FET...) la ligne contient un nom de modèle qui renvoie à une description plus détaillée des caractéristiques du composant (voir § 5.10 page 23). Il existe des bibliothèques décrivant les modèles d'un grand nombre de composants tels que diodes, transistors, AOP, etc. Ces modèles peuvent être facilement incorporés dans le fichier-circuit pour compléter la description.

#### 4.3 – Commandes d'analyses

Le tableau IV page 31 résume les différentes analyses qui peuvent être réalisées sur un circuit. Comme toutes les commandes, elles sont identifiées par un mot-clé qui commence par un point (.) et suivent une syntaxe propre à chacune d'elle. Ces analyses peuvent être classées en trois catégories principales :

- Analyses en continu : par nature indépendantes du temps, ne concernent que le comportement statique du circuit (les condensateurs sont considérés comme des circuits ouverts, les inductances comme des courts-circuits). Ces analyses tiennent compte des éventuelles non-linéarités statiques des caractéristiques des composants.

- Analyses dynamiques : elles concernent le comportement en fonction de la fréquence de circuits linéaires ou de circuits non linéaires préalablement linéarisés au voisinage d'un point de polarisation statique. Les variables concernées sont des nombres complexes qui peuvent être exprimés sous forme réel et imaginaire ou sous forme module et argument.

- Analyses temporelles : elles décrivent le comportement d'un circuit généralement non linéaire en fonction du temps à partir de l'état de polarisation calculé à l'instant initial t=0

Ces analyses de base peuvent être complétées par la variation de paramètres, une analyse pourra ainsi être répétée pour différentes valeurs d'un composant, d'un paramètre d'analyse ou de la température. De même l'effet de la dispersion des caractéristiques des composants pourra être évalué en donnant à un ou plusieurs composants une série de valeurs tirées au hasard dans l'intervalle de tolérance.

```

.OP

.DC Ve -1 +1 0.1

.AC dec 21 1 1MEG

.TRAN 50u 5m

.STEP param Cvar LIST 100n, 220n, 470n, 680n, 1000n

```

#### 4.4 – Commandes de contrôle

En plus des commandes d'analyse, SPICE dispose d'un certain nombre de commandes permettant de fixer l'état initial des composants, de définir les caractéristiques des composants non linéaires, de structurer le fichier-circuit, de préciser la nature et la forme des variables à éditer, etc. Ces commandes sont résumées dans le tableau V page 32.

```

Exemples:

.OP

.PROBE

.PARAM vmax=10

.IC v(3)=0.1

.MODEL ca3086 NPN BF=175 VAF=50 CJE=5p CJC=3p

.END

```

#### 5 - Syntaxe SPICE

#### 5.1 – Conventions typographique

#### 5.2 - Calcul du point de polarisation (.OP)

Forme générale : .OP

L'instruction .OP permet l'édition d'informations détaillées sur le point de polarisation. Le point de polarisation est calculé même s'il n'y a pas d'instruction .OP. Sans l'instruction .OP, la seule information éditée concernant le point de polarisation est une liste des tensions de nœuds. Avec une instruction .OP, les courants et les puissances dissipées par toutes les sources de tension sont édités. De même, l'état de polarisation et les paramètres petits signaux (linéarisés) de toutes les sources commandées et de tous les composants semi-conducteurs sont également édités. L'instruction .OP commande uniquement l'édition des informations du point de polarisation normal. C'est l'instruction .TRAN qui commande l'édition des informations concernant le point de polarisation de l'analyse en transitoire.

#### 5.3 - Analyse en continu (.DC)

Formes générales:

```

.DC [LIN] <nom de variable> <valeur de départ> <valeur de fin> + <incrément> [spécification de balayage imbriqué]

.DC [OCT] [DEC] <nom de variable> <valeur de départ> <valeur de fin> + <nb. de points> [spécification de balayage imbriqué]

.DC <nom de variable> LIST <valeur>* [spécification de balayage imbriqué]

```

```

DC VIN -.25 .25 .05

DC LIN I2 5mA -2mA 0.1mA

DC VCE OV 10V .5V IB 0mA 1mA 50uA

DC RES RMOD(R) 0.9 1.1 .001

DC DEC NPN QFAST(IS) 1E-18 1E-14 5

DC TEMP LIST 0 20 27 50 80 100 -50

DC PARAM Valim 7.5 15 .5

```

L'instruction .DC réalise un balayage pour une analyse en courant continu sur le circuit. Le balayage en courant continu calcule le point de polarisation du circuit sur une gamme donnée de valeurs de *<nom de variable>*. Un balayage imbriqué est disponible. Une seconde variable, type de balayage, valeur de début, valeur de fin et incrément peuvent être placés à la suite du premier balayage. Dans ce cas, le premier balayage constituera la boucle « intérieure » : le balayage complet de la première variable sera réalisé pour chaque valeur du second balayage. Les règles pour les valeurs du second balayage sont identiques à celles du premier.

Le balayage peut être linéaire, logarithmique ou constitué d'une liste de valeurs. Si le balayage est linéaire, le mot-clé LIN est optionnel. Le type de balayage peut être :

- LIN Balayage linéaire. La variable est balayée linéairement de la valeur de départ à la valeur de fin. *<incrément>* est la valeur du pas utilisé.

- OCT Balayage par octaves. La variable est balayée logarithmiquement par octaves. < nb.  $de\ points > indique$  le nombre de points par octave.

- DEC Balayage par décades. La variable est balayée logarithmiquement par décades. < nb.  $de\ points >$  indique le nombre de points par décade.

- LIST Utilise une liste de valeurs. Dans ce cas il n'y a pas de valeurs de départ ni de fin. À la place, la variable prendra successivement les valeurs qui suivent le mot-clé LIST.

#### 5.4 - Analyse en alternatif petits signaux (.AC)

Formes générales:

.AC [LIN] [OCT] [DEC] < nb. de points > < fréquence de départ > < fréquence de fin >

```

Exemples: AC LIN 101 100Hz 200Hz

AC OCT 10 1KHz 16KHz

AC DEC 20 1MEG 100MEG

```

L'instruction .AC est utilisée pour calculer la réponse en fréquence d'un circuit sur une gamme de fréquences. Les arguments LIN, OCT, ou DEC sont des mots-clés qui spécifient le type de balayage et  $< nb.\ de\ points>$  indique le nombre de points utilisés au cours du balayage :

- LIN Balayage linéaire. La fréquence est balayée linéairement entre les fréquences de départ et de fin. < nb. de points > est le nombre total de points dans le balayage.

- OCT Balayage par octaves. La fréquence est balayée de manière logarithmique par octaves. <nb. de points> indique le nombre de points par octave.

- DEC Balayage par décades. La fréquence est balayée de manière logarithmique par décades. <nb. de points> indique le nombre de points par décade.

#### 5.5 - Analyse temporelle (.TRAN)

Forme générale:

- $.\, {\tt TRAN[/OP]} < intervalle \,\, d'\'{e}dition > < temps \,\, final > \,\, [< d\'{e}lai \,\, avant \,\, \'{e}dition > \,\,$

- + [incrément maximal]] [SKIPBP] [UIC]

Exemples: .TRAN 1ns 100ns .TRAN/OP 1ns 100ns 20ns SKIPBP .TRAN 1ns 100ns 0ns .1ns

L'instruction .TRAN permet l'exécution d'une analyse en transitoire sur le circuit. L'analyse en transitoire calcule le comportement du circuit au cours du temps en commençant à la valeur TIME = 0 jusqu'à la valeur < temps final>. L'analyse en transitoire utilise un incrément de temps interne qui est ajusté au cours de l'analyse. Sur les intervalles où il y a peu d'activité, l'incrément de temps interne est augmenté, il est au contraire réduit pendant les intervalles actifs. L'<intervalle d'édition> est l'intervalle de temps utilisé pour l'édition des résultats de l'analyse transitoire par les instructions .PRINT et .PLOT. Du fait que les calculs ne sont pas effectués aux mêmes instants que les résultats édités, ces derniers sont obtenus par une interpolation polynomiale du second ordre. L'analyse en transitoire commence toujours à la valeur TIME = 0. Cependant il est possible de supprimer l'édition d'une partie de l'analyse. Le  $[d\'elai\ avant\ \'edition]$  représente la durée d'analyse (depuis TIME = 0) qui n'est ni éditée ni donnée à Probe. On est quelquefois intéressé par la valeur de l'incrément de temps interne. La valeur maximale de cet incrément est égal à < tempsfinal>/50 (ce n'est pas l'<intervalle d'édition>). L'[incrément maximal] permet d'attribuer à l'incrément de temps interne une valeur maximale différente de celle de l'intervalle d'édition. Avant de réaliser l'analyse en transitoire, PSpice calcule un point de polarisation du circuit indépendamment du point de polarisation normal. Il en est ainsi parce que les sources de tension indépendantes peuvent avoir une valeur de départ différente pour l'analyse temporelle et pour l'analyse en courant continu. Normalement, seules les tensions de nœuds sont éditées pour le point de polarisation de l'analyse en transitoire. Cependant le suffixe « /OP » (après .TRAN) produira la même édition détaillée du point de polarisation que l'instruction .OP pour le point de polarisation normal. Si le mot-clé SKIPBP (sauter le calcul de polarisation) ou UIC (utiliser les conditions initiales) est ajouté à la fin de l'instruction .TRAN, le calcul du point de polarisation n'est pas effectué. Ces arguments sont utilisés avec la spécification IC= pour les éléments réactifs (condensateurs et inductances).

#### 5.6 - Relations entre instructions

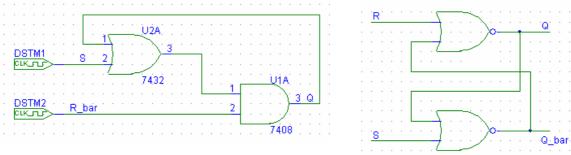

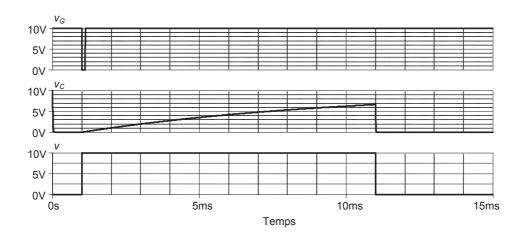

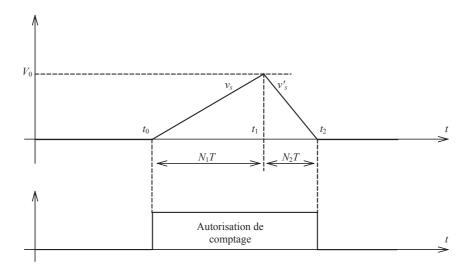

Chaque source de tension ou de courant indépendante comporte des paramètres qui précisent son utilisation avec les différentes analyses. La figure 8 illustre les relations qui existent entre la description de la source Ve et les analyses effectuées :

- L'analyse .OP ne tient compte que de l'argument DC=1V pour effectuer le calcul du point de polarisation.

- L'analyse .AC calcule d'abord le point de polarisation à partir de l'argument DC=1V pour établir le schéma équivalent linéaire puis réalise l'analyse dynamique à partir de l'argument AC=1.

L'analyse .TRAN ne tient compte que de la spécification temporelle de la source si elle existe, ici : SIN(0 100V 50Hz). Lorsqu'il n'y a pas de spécification temporelle, c'est l'argument DC=... qui est utilisé.

```

| Ve 1 0 | DC=1V | AC=1 SIN(0 100V 50Hz) | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... | ... |

```

Fig. 8 – Relations entre analyses et paramètres de sources.

#### 5.7 – Édition des résultats

PSpice dispose de trois instructions pour éditer les résultats d'analyse (cf. tableau V page 32) : .PLOT, .PRINT et .PROBE. L'instruction .PLOT qui permet l'affichage graphique en caractères alphanumériques dans le fichier de sortie, devenue obsolète avec l'utilisation de *Probe*, ne sera pas décrite ici.

#### Forme générale de .PRINT

```

.PRINT [DC] [AC] [NOISE] [TRAN] [variable\ de\ sortie]*

```

L'instruction .PRINT permet l'édition des résultats des analyses en courant continu, dynamique, bruit et transitoire sous la forme de tableaux appelées tableaux de sortie. Seules les analyses de type .DC, .AC, .NOISE et .TRAN peuvent être éditées avec l'instruction .PRINT. Un et un seul type d'analyse doit être spécifié.

#### Formes générales de .PROBE

```

.PROBE [variable\ de\ sortie]*

```

L'instruction .PROBE écrit les résultats des analyses en courant continu, dynamique et transitoire dans un fichier appelé nom. dat qui sera utilisé par le post-processeur graphique Probe.

La première forme (celle qui ne comporte pas de variable de sortie) écrit toutes les tensions de nœuds et tous les courants de composants dans le fichier de sortie. La seconde forme n'écrit que les variables spécifiées dans la liste. Noter que contrairement aux instructions .PRINT et .PLOT, il n'y a pas à préciser de type d'analyse avant la liste des variables.

#### Format des variables de sortie pour les instructions : .PLOT, .PRINT, .PROBE

La nature des variables utilisées dépend du type d'analyse réalisée et du composant étudié. Ainsi, une analyse en courant continu ou temporelle utilise des variables réelles tandis qu'une analyse dynamique traite des variables complexes. Le tableau VI page 33 résume la syntaxe à utiliser pour éditer les résultats selon le composant et le type d'analyse réalisée et le tableau VII page 34 donne quelques exemples d'utilisation (voir également les exemples ci-dessus).

#### 5.8 – Expressions et opérateurs

Dans de nombreux cas PSpice autorise l'utilisation d'expressions mathématiques qui facilitent la description des circuits ou qui permettent la création de composants « comportementaux » non linéaires par exemple. Lorsqu'une expression est utilisée dans une instruction elle doit être placée entre accolades :  $\{<expression>\}$ .

Une expression peut comporter des constantes, des variables, des opérateurs et des fonctions. Les tableaux VIII page 34 et IX page 35 résument les différents opérateurs et les différentes fonctions reconnus par PSpice.

#### 5.9 - Sources

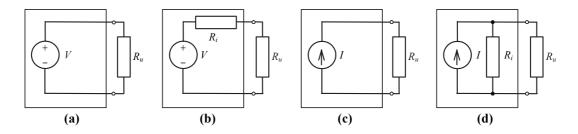

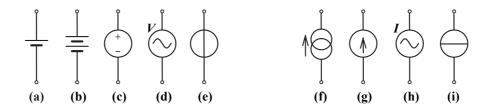

SPICE dispose de deux types de source : les sources indépendantes (courant ou tension) et les sources commandées (courant ou tension).

#### Sources indépendantes: I source de courant, V source de tension

Formes générales :

```

\begin{split} & \text{I} < nom > < nœud + > < nœud - > [[DC] < valeur >] \text{ [AC } < amplitude > [phase]] \\ & + [sp\'{e}cifications \ de \ transitoire] \\ & \text{V} < nom > < nœud + > < nœud - > [[DC] < valeur >] \text{ [AC } < amplitude > [phase]] \\ & + [sp\'{e}cifications \ de \ transitoire] \end{split}

```

L'élément I est une source de courant, l'élément V est une source de tension. Dans les deux cas le courant positif circule dans la source du nœud (+) vers le nœud (-). La valeur

par défaut est zéro pour les spécifications DC, AC ou transitoire. On peut indiquer une quelconque des trois spécifications ou deux d'entre elles ou toutes ou même aucune. La phase de la spécification AC est exprimée en degrés.

Si l'on spécifie un mode transitoire, ce doit être l'un des mots-clés suivants :

Les différents paramètres des formes de signaux sont décrits dans les tableaux des paragraphes suivants, la colonne **PSpice** indique le mot-clé utilisé par **PSpice** pour définir la variable utilisée dans les relations de définition.

| Paramètre | PSpice | Définition                                 | Défaut              | Unité  |

|-----------|--------|--------------------------------------------|---------------------|--------|

| $v_1$     | v1     | Valeur initiale 1 <sup>ère</sup> phase     |                     | V ou A |

| $v_2$     | v2     | Valeur asymptotique 1 <sup>ère</sup> phase |                     | V ou A |

| $t_{d1}$  | td1    | Délai initial                              | 0                   | s      |

| $	au_1$   | tau1   | Constante de temps 1 <sup>ère</sup> phase  | $t_{step}$          | s      |

| $t_{d2}$  | td2    | Délai avant 2 <sup>ème</sup> phase         | $t_{d1} + t_{step}$ | s      |

| $	au_2$   | tau2   | Constante de temps 2 <sup>ème</sup> phase  | $t_{step}$          | s      |

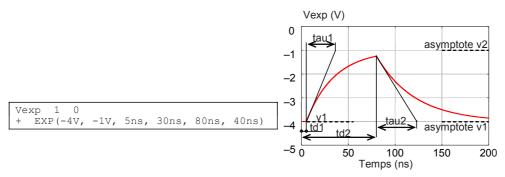

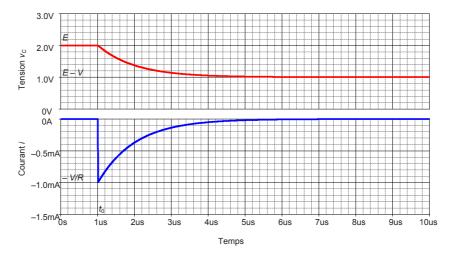

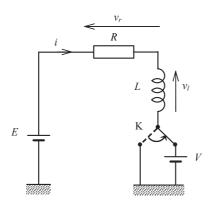

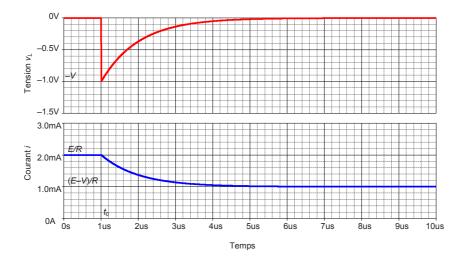

Fig. 9 – Exemple de source exponentielle et paramètres de l'instruction EXP.

#### Spécifications temporelles de la forme exponentielle (EXP)

EXP(

$$< v_1 > < v_2 > < t_{d1} > < \tau_1 > < t_{d2} > < \tau_2 >$$

)

Expressions des différentes phases (Fig. 9) :

$$\begin{array}{lll} 0\leqslant t\leqslant t_{d1} & : & v(t)=v_{1}\\ t_{d1}\leqslant t\leqslant t_{d2} & : & v(t)=v_{1}+(v_{2}-v_{1})[1-\exp\left(-(t-t_{d1})/\tau_{1}\right)]\\ t\geqslant t_{d2} & : & v(t)=v_{1}+(v_{2}-v_{1})\{[1-\exp\left(-(t-t_{d1})/\tau_{1}\right)]\\ & & -[1-\exp\left(-(t-t_{d1})/\tau_{1}\right)]\} \end{array}$$

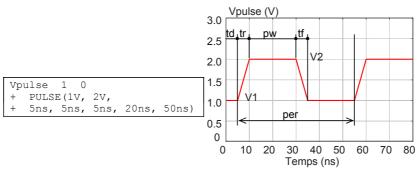

#### Spécifications temporelles de la forme impulsionnelle (PULSE)

PULSE(

$$< v_1 > < v_2 > < t_d > < t_r > < t_f > < w > < T >$$

)

Valeur de la source dans les différentes phases (Fig. 10) :

| Paramètre | PSpice | Définition                             | Défaut     | Unité  |

|-----------|--------|----------------------------------------|------------|--------|

| $v_1$     | v1     | Valeur initiale 1 <sup>ère</sup> phase |            | V ou A |

| $v_2$     | v2     | Valeur finale 1 <sup>ère</sup> phase   |            | V ou A |

| $t_d$     | td     | Délai initial                          | 0          | s      |

| $t_r$     | tr     | Temps de montée                        | $t_{step}$ | s      |

| $t_f$     | tf     | Temps de descente                      | $t_{step}$ | s      |

| w         | pw     | Largeur d'impulsion                    | $t_{stop}$ | s      |

| T         | per    | Période                                | $t_{stop}$ | s      |

Fig. 10 – Exemple de source impulsionnelle et paramètres de l'instruction PULSE.

```

\begin{array}{lll} t = 0 & : & v(t) = v_1 \\ t = t_d & : & v(t) = v_1 \\ t = t_d + t_r & : & v(t) = v_2 \\ t = t_d + t_r + w & : & v(t) = v_2 \\ t = t_d + t_r + w + t_f & : & v(t) = v_1 \\ t = t_{stop} & : & v(t) = v_1 \end{array}

```

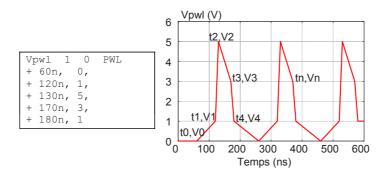

Fig. 11 – Exemple de source linéaire par morceaux.

#### Spécifications temporelles de la forme linéaire par morceaux (PWL)

PWL(

$$< t_0 > < v_0 > < t_1 > < v_1 > < t_2 > < v_2 > \dots < t_n > < v_n >$$

)

Chaque couple de valeurs  $(t_i, v_i)$  indique qu'à l'instant  $t_i$  la tension ou le courant de la source vaut  $v_i$  (en volt ou ampère). Les valeurs intermédiaires sont déterminées par interpolation linéaire entre les valeurs limites (Fig. 11).

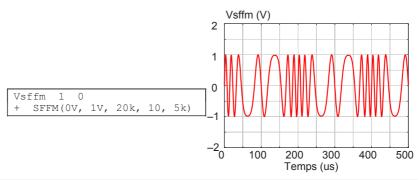

Spécifications temporelles de la forme sinusoïdale modulée en fréquence (SFFM)

$${\tt SFFM(} < v_0 > < v_a > < m > < f_s > {\tt )}$$

1.5 Vsin (V)

| Paramètre | PSpice | Définition              | Défaut       | Unité  |

|-----------|--------|-------------------------|--------------|--------|

| $v_0$     | v0     | Valeur d'offset         |              | V ou A |

| $v_a$     | va     | Amplitude               |              | V ou A |

| $f_c$     | fc     | Fréquence porteuse      | $1/t_{stop}$ | Hz     |

| m         | mdi    | Indice de modulation    |              |        |

| $f_s$     | fs     | Fréquence de modulation | $1/t_{stop}$ | Hz     |

Fig. 12 – Exemple de source sinusoïdale modulée en fréquence et paramètres de l'instruction SFFM.

SIN(0V, 1V, 100meg, 2n)

|   | Vdamp    | 1         | 0   | SIN(OV,  | 1V, | 100meg,              | 2n,  | 5e7) |                        |  |

|---|----------|-----------|-----|----------|-----|----------------------|------|------|------------------------|--|

|   |          |           |     |          |     | 1.5 <mark>V</mark> ( | damp | (V)  | ,                      |  |

| a | 1 = 0    |           | (a) |          |     | 1.5                  |      | thet | ta = 5.10 <sup>7</sup> |  |

|   | $\wedge$ | $\Lambda$ | 1 / | <b>\</b> |     | 1.0                  | _    |      |                        |  |

Fig. 13 – Exemple de source sinusoïdale non amortie (a), amortie (b) et paramètres de l'instruction SIN.

Expression analytique (Fig. 12):

$$v(t) = v_0 + v_a \sin[2\pi f_c t + m \sin(2\pi f_s t)]$$

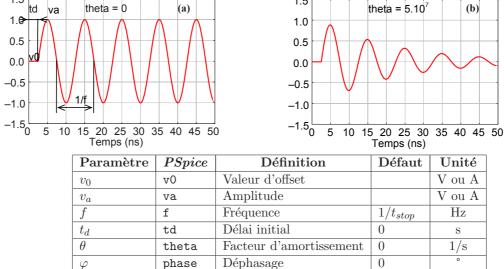

Spécifications temporelles de la forme sinusoïdale (SIN)

SIN(

$$< v_0 > < v_a > < f > < t_d > < heta > < arphi >$$

)

Expressions des différentes phases (Fig. 13) :

```

0 \le t \le t_d : v(t) = v_0

t \ge t_d : v(t) = v_0 + v_a \sin\{2\pi[f(t - t_d) + \varphi/360]\} \exp[-(t - t_d)\theta]

```

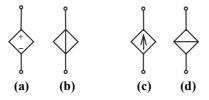

#### Sources commandées

Il existe à l'origine quatre types de sources commandées :

- E source de tension commandée en tension,

- F source de courant commandée en courant,

- G source de courant commandée en tension,

- H source de tension commandée en courant.

À cause des extensions de syntaxe pour la modélisation comportementale non linéaire apportées par *PSpice*, il n'est plus nécessaire de différencier le type de commande au niveau de la définition du composant, il suffit de distinguer la nature de la source (tension E ou courant G) et de préciser le type de commande (courant, tension ou autre) dans les arguments, c'est pourquoi les sources F et H sont devenues obsolètes et ne seront pas décrites ici.

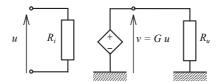

Les sources de courant commandées (G) ont la même syntaxe que les sources de tension, substituer simplement la lettre G à la lettre E.

Formes générales :

```

E < nom > < nom d + > < nom d - >

+ < n \approx ud \ de \ commande + > < n \approx ud \ de \ commande - > [gain]

E < nom > < nom d + > < nom d - > VALUE = { < expression > }

E < nom > < noed + > < noed - > TABLE \{ < expression > \} =

+ < <valeur d'entrée>, <valeur de sortie> >*

E < nom > < noed + > < noed - > LAPLACE {< expression >} = {< transformation >}

E < nom > < nowd + > < nowd - > FREQ \{ < expression > \} = [mot-clé]

+ < < fréquence > , < amplitude , < phase > > * [DELAY = < délai > ]

E < nom > < nowd + > < nowd - > CHEBISHEV \{ < expression > \} =

+ < [LP] [HP] [BP] [BR] >, < fréquences de coupures >*, < atténuation >*

Ebuff 1 2 10 11 1.0

Erac 5 0 VALUE={5V*sqrt(V(3,2))}

Et2 2 0 TABLE \{V(4,7)\}=(0,0) (30,1)

Erc 5 0 LAPLACE \{V(10)\}=\{1./(1.+.001*s)\}

Epb 5 0 FREQ \{V(10)\}=(0,0,0)(5kHz,0,0)(6kHz,-60,0) DELAY=3.2ms

Exemples:

Epb 5 0 CHEBISHEV {V(10)}=LP 800 1.2kHz .1dB 50dB

Gbuff 1 2 10 11 1.0

Gpsk 11 6 VALUE={5mA*SIN(6.28*10kHz*TIME+v(3))}

Gt 5 7 VALUE=\{200E-6*PWR(V(1)*V(2),1.5)\}

Gperte 5 0 LAPLACE {V(10)}={EXP(-sqrt(C*s*(R+L*s)))}

```

La première forme et le premier exemple s'appliquent au cas linéaire. Les nœuds (+) et (-) sont les nœuds de sortie. Le courant est compté positivement lorsqu'il circule dans la

source du nœud (+) vers le nœud (-). Les nœuds (commande +) et (commande -) vont par paires et définissent un ensemble de tensions de commande. Un nœud particulier peut apparaître plusieurs fois et il n'est pas nécessaire que les nœuds de sortie et de commande soient différents. Dans le cas linéaire, il y a deux nœuds de commande suivis de la valeur du gain.

La forme TABLE peut comporter jusqu'à 2048 paires de valeurs d'entrée/sortie.

Consulter la documentation pour l'utilisation des sources commandées dans les autres cas.

#### 5.10 – Modèles de composants

Les composants passifs sont le plus souvent décrits par une seule valeur numérique (valeur de la résistance, du condensateur, etc.), cette valeur fait alors partie de la description du composant comme le montre la figure 2 page 7 par exemple. Cependant, le comportement d'un composant passif peut nécessiter une description plus complète : coefficient de température, tolérance de fabrication, etc. Ces informations pourraient figurer dans l'instruction de description mais elles l'alourdiraient et surtout il serait nécessaire de les répéter pour tous les composants même si leurs caractéristiques sont identiques. D'où l'intérêt de disposer d'un « modèle » auquel peuvent être référencés un ou plusieurs composants ce qui évite la répétition des caractéristiques. Pour les composants semi-conducteurs (diodes, BJT, FET, MOS...) ou plus généralement tous les composants ne pouvant pas être décrits par une simple valeur numérique, la référence à un modèle est non seulement utile mais elle est obligatoire. Au lieu d'une valeur numérique, le composant est décrit par un < nom >de modèle qui renvoie à la commande . MODEL qui porte le même < nom >. Dans l'exemple ci-dessous, le composant D1 est une diode branchée entre les nœuds 1 et 2 décrite par le modèle « diode », ce nom est arbitraire, il peut être formé de n'importe quelle chaîne alphanumérique ne contenant pas de séparateur. Lorsque l'interpréteur de commandes rencontre cette instruction il recherche la commande .MODEL portant la même référence. Cette instruction précise le <type> de composant décrit par un mot-clé réservé dont la liste est donnée dans le tableau III page 31 où l'on voit qu'un même composant peut avoir différents  $\langle types \rangle$  ce qui explique la nécessité de le préciser dans le modèle. Dans l'exemple ci-dessous, on remarque que plusieurs composants peuvent référencer le même modèle (diodes D1 et D2) et que la description des composants passifs peut également être complétée par un modèle.

```

Exemples: | Vin 1 0 SIN(0 10V 50Hz) | D1 1 2 | diode | D2 2 1 | diode | R 2 0 | modR | 1 | C 2 0 | modC | 1 | .MODEL | diode | D (IS=1e-12) | .MODEL | modR | RES (R=1k Tc1=.02) | .MODEL | modC | CAP (C=1000u)

```

Forme générale:

```

.MODEL < nom> < type> ([< nom de paramètre>=< valeur> + [spécification de tolérance]]*)

```

```

Autres exemples:

.MODEL RMAX RES (R=1.5 TC1=.02 TC2=.005)

.MODEL DNOM D (IS=1E-9)

.MODEL QDRIV NPN (IS=1E-7 BF=30)

.MODEL MLOAD NMOS (LEVEL=1 VT0=.7 CJ=.02PF)

.MODEL CMOD CAP (C=1 DEV 5%)

.MODEL DLOAD D (IS=1E-9 DEV .5% LOT 10%)

```

Chaque composant dispose d'un nombre parfois important de paramètres de modèle décrits dans la documentation SPICE qui devra être consultée pour en connaître la signification. Les principaux paramètres de modèle des composants semi-conducteurs sont décrits dans les chapitres qui leur sont consacrés.

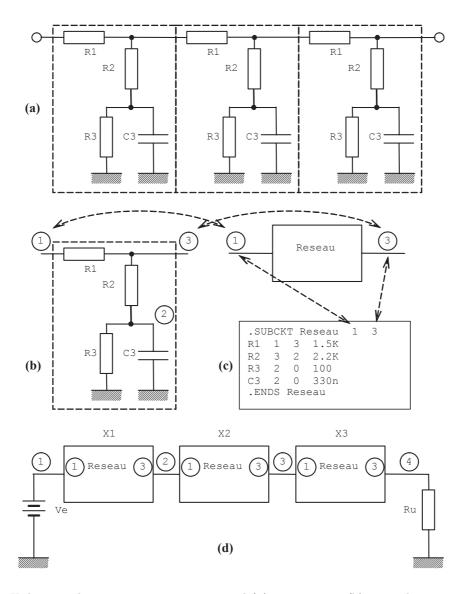

#### 5.11 – Sous-circuits

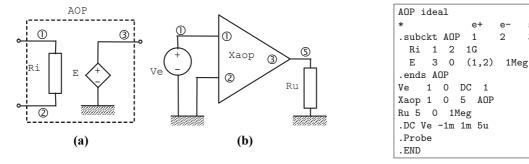

**Fig. 14** – Utilisation de sous-circuits, circuit initial (a), sous-circuit (b), texte du sous-circuit (c), circuit final (d).

La notion de sous-circuit est analogue à la notion de sous-programme des langages informatiques, elle permet de structurer un fichier-circuit en blocs qui peuvent être réutilisés dans le même fichier-circuit ou réunis dans une bibliothèque de sous-circuits pour être utilisés dans un autre fichier-circuit. Un bloc de sous-circuit est encadré par les commandes .SUBCKT et .ENDS et il est appelé comme un composant dont l'identificateur commence par la lettre X.

Forme générale de définition du sous-circuit :

```

.SUBCKT < nom\ du\ sous\text{-}circuit> < nœud>* \\ ... < sous\text{-}circuit> \\ .ENDS\ [nom\ du\ sous\text{-}circuit]

```

L'instruction .SUBCKT commence la définition d'un sous-circuit. Cette définition se termine avec une instruction .ENDS. Toutes les instructions comprises entre .SUBCKT et .ENDS font partie de la définition. Chaque fois qu'un sous-circuit est appelé, par une instruction  $\mathtt{X}$ , toutes les instructions de la définition remplacent l'instruction appelante.  $< nom \ du \ sous-circuit>$  est le nom utilisé par l'instruction  $\mathtt{X}$  pour référencer le sous-circuit. Il doit commencer par une lettre.

< næud>\* est une liste de nœuds. Il doit y avoir autant de nœuds dans l'instruction appelant le sous-circuit que dans la définition de celui-ci. Lorsque le sous-circuit est appelé, les nœuds réels (ceux de l'instruction appelante) remplacent les nœuds arguments (ceux de l'instruction de définition).

Les appels de sous-circuits peuvent être imbriqués. C'est-à-dire qu'une instruction X peut apparaître entre un .SUBCKT et un .ENDS. Les définitions de sous-circuits **ne peuvent pas être imbriquées**, une instruction .SUBCKT ne peut pas apparaître entre un .SUBCKT et un .ENDS.

Les définitions de sous-circuits ne devraient contenir que des instructions de description de composants (instructions sans « . » initial) avec toutefois la possibilité d'utiliser des instructions .MODEL. Les modèles définis dans une définition de sous-circuit ne sont accessibles que dans la définition du sous-circuit dans lequel ils apparaissent. Par contre, si une instruction .MODEL apparaît dans le circuit principal, ce modèle est accessible dans le circuit principal et dans tous les sous-circuits. Les noms de nœuds, de composants et de modèles sont locaux au sous-circuit dans lequel ils sont définis. C'est-à-dire qu'il est correct d'utiliser dans un sous-circuit un nom qui a déjà été utilisé dans le circuit principal. Lorsque le sous-circuit est utilisé, tous les noms qui y figurent sont préfixés par le nom du sous-circuit, par exemple : «Q13 » devient «X3.Q13 ». Après développement, tous les noms sont uniques.

Forme générale de l'appel de sous-circuit :

```

X < nom > < nœud > * < nom du sous-circuit >

```

Le <nom du sous-circuit> est le nom utilisé dans la définition du sous-circuit (voir l'instruction .SUBCKT). Il doit y avoir le même nombre de nœuds dans l'appel et dans la définition. Lorsque cette instruction est rencontrée, le sous-circuit référencé est importé dans le circuit et les nœuds indiqués en arguments de la définition sont remplacés par les nœuds réels de l'instruction appelante. Elle permet de définir une seule fois un bloc de circuit et d'utiliser ce bloc à plusieurs endroits.

Les appels de sous-circuits peuvent être imbriqués. C'est-à-dire qu'il est possible de faire un appel à un sous-circuit A dont la définition contient un appel à un sous-circuit B. Le niveau d'imbrication peut être quelconque mais **pas circulaire**. Par exemple, si la définition du sous-circuit A contient un appel au sous-circuit B, alors la définition du sous-circuit B ne doit pas contenir d'appel au sous-circuit A.

Exemple : la figure 14.a page 24 représente un circuit contenant trois cellules identiques. Cette cellule peut être décrite dans un sous-circuit appelé Reseau (Fig. 14.b et 14.c) et utilisée en trois exemplaires dans le circuit principal (Fig. 14.d et Fig. 15).

Noter que le sous-circuit Reseau comporte 3 nœuds internes dont deux (1 et 3) sont accessibles de l'extérieur, noter également la composition du circuit principal et l'appel aux sous-circuits par l'instruction X. Les extensions propres à *PSpice* permettent également le passage de paramètres dans un sous-circuit comme l'illustre la figure 16, cette possibilité permet la constitution de sous-circuits sans que la valeur des composants internes soit connue *a priori*. Pour plus de détail sur l'utilisation des paramètres dans *PSpice*, consulter la documentation.

```

* Sous circuits *

.SUBCKT Reseau 1

R1 1 3 1.5K

R2 3 2

2.2K

R3 2 0 100

C3 2 0 330n

.ENDS Reseau

1 0 1V

Vе

Х1

1

2

Reseau

3 Reseau

Х.З

3

4 Reseau

Ru

4

0

120

ΠP

.DC Ve 0 20 5

Print DC I(X1.R1) I(X3.R2) I(Ru)

```

Fig. 15 – Fichier-circuit de la figure 14.d.

```

.SUBCKT Reseau 1 3 params: rval1=1k rval2=1k rval3=1k cval3=100n

R1 1 3 {rval1}

R.2

3 2

{rval2}

R3 2 0

{rval3}

C3 2 0 {cval3}

.ENDS Reseau

Ve

1 0 1V

Reseau params: rval1=1.5k rval2=2.2k rval3=100 cval3=330n

Х2

Reseau params: rval1=2.2k rval2=3.3k rval3=220 cval3=100n

X3 3 4

Reseau params: rval1=1k rval2=4.7k rval3=330 cval3=470n

.OP

.DC Ve 0 20 5

.Print DC I(X1.R1) I(X3.R2) I(Ru)

```

Fig. 16 – Autre fichier-circuit de la figure 14.d.

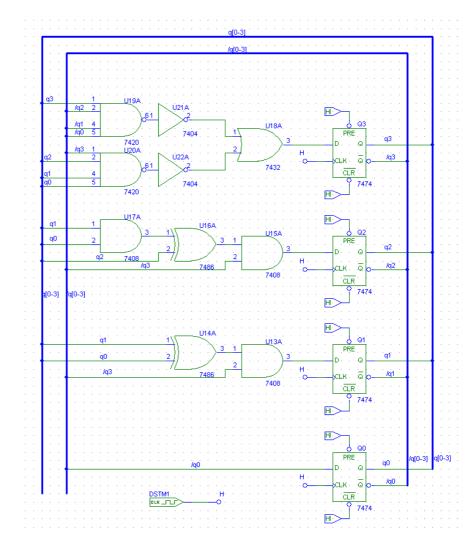

#### 6 - Simulation des circuits logiques

#### 6.1 – Fichier-circuit ou saisie de schéma?

Il est possible de simuler le comportement des circuits numériques avec PSpice A/D (A/D signifie Analog/Digital). Jusqu'à maintenant les circuits analogiques qui ont été simulés étaient décrits grâce à un fichier-circuit. Comme on l'a vu au § 2.2 page 5, il est également possible de décrire graphiquement le circuit en utilisant l'utilitaire Schematics de saisie de schéma disponible dans le logiciel PSpice. Très souvent il est beaucoup plus rapide d'utiliser un fichier texte plutôt qu'une représentation graphique pour la description des circuits analogiques, en revanche les circuits numériques nécessitent la description d'un si grand nombre de paramètres et de connexions que la description textuelle devient rapidement fastidieuse et difficile à corriger en cas d'erreur. Dans ce cas, la saisie de schéma s'avère un outil quasi indispensable. L'appel de l'utilitaire Schematics ouvre une fenêtre comme le montre la figure 17.

Fig. 17 – Fenêtre de l'utilitaire « Schematics ».

#### 6.2 - Porte Nand

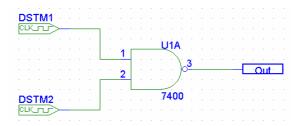

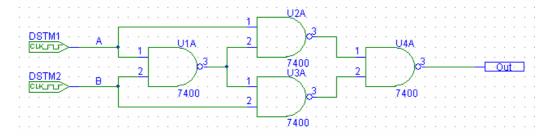

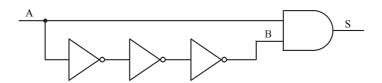

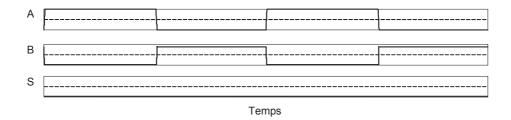

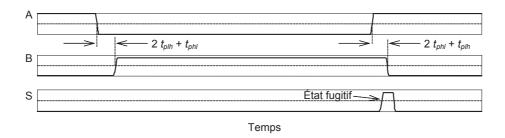

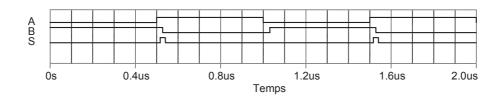

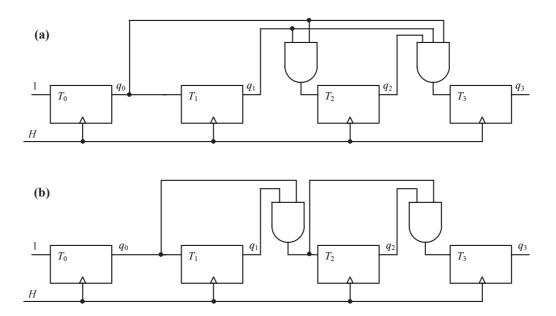

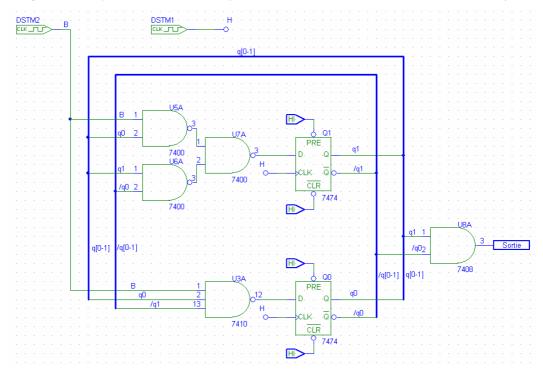

Pour illustrer sommairement la simulation numérique, prenons le cas du circuit logique représenté sur la figure 18. Il peut être réalisé en utilisant les commandes successives :

- Draw>Get New Part>7400>Place & Close (ou cliquer sur 🛅) pour placer la porte,

- Draw>Get New Part>Global>Place & Close, pour placer le port de sortie,

- Ctrl-R, pour pivoter le port,

- Draw>Get New Part>DigClock>Place & Close, pour placer deux horloges,

- Draw>Wire (ou cliquer sur ) pour connecter les différents composants.

Fig. 18 – Schéma d'un circuit à porte NAND.

La plupart des commandes précédentes peuvent être réalisées grâce aux différents boutons de la barre d'outils affichée en haut de la fenêtre. Le composant appelé 7400 est une porte Nand TTL à deux entrées, Global est un port qui permet d'identifier ou d'accéder à un signal dans un circuit. Pour donner un label à un port, il suffit de double-cliquer sur le symbole (ou d'entrer la commande Edit>Attributes) et remplir la boîte de dialogue avec le label choisi (ici le label est out). Les deux composants DigClock produisent les signaux d'entrée nécessaires pour vérifier le comportement de la porte Nand. Pour ajuster les caractéristiques des sources il suffit de double-cliquer sur chaque symbole (ou d'entrer la commande Edit>Attributes) et de régler les paramètres ontime et offtime de chaque horloge dans la boîte de dialogue. Ici ces paramètres valent tous les deux respectivement 200 ns pour DSTM1 et 100 ns pour DSTM2. Pour simuler le circuit il faut tout d'abord sauvegarder le schéma réalisé (commande :  $File > Save\ As$  ou cliquer sur  $|\blacksquare|$ ) sous le nom choisi (nom.sch). Les caractéristiques de l'analyse temporelle peuvent alors être décrites grâce à la boîte de dialogue ouverte par la commande *Analysis>Setup* (ou cliquer sur [2]). En cliquant sur le bouton Transient, il est possible de renseigner les champs Print Step et Final Time, par exemple 10 ns et 600 ns dans l'exemple donné. Pour lancer l'analyse, entrer simplement la commande : Analysis>Simulate (ou appuyer sur la touche F11 ou cliquer sur

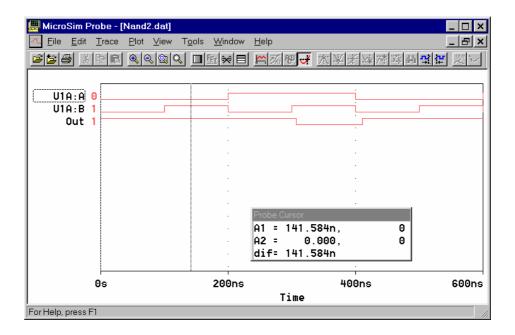

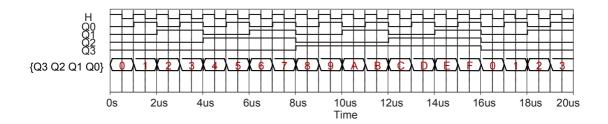

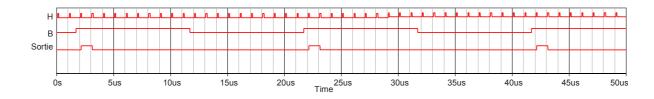

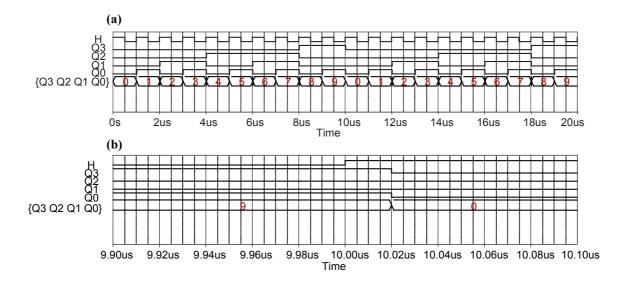

Lorsque l'analyse est terminée, la fenêtre du post-processeur graphique *Probe* s'ouvre automatiquement et il est possible de tracer les signaux d'entrée et de sortie comme le montre la figure 19. L'utilisation des curseurs permet de vérifier la table de vérité de la porte et de mettre en évidence les aléas de fonctionnement liés aux retards des signaux dans la porte.

#### 7 - Recommandations

Quelles que soient les performances du logiciel, la richesse des bibliothèques et la fidélité des modèles elles ne sauraient en aucun cas *remplacer* le sens critique de l'utilisateur. Pour utiliser efficacement le simulateur il convient de garder en mémoire et d'appliquer un petit nombre de règles simples mais importantes :

- Avant d'exécuter la simulation d'un circuit, effectuer une estimation même grossière des valeurs ou des sens de variation des grandeurs recherchées avec des modèles de comportement simplifiés à l'extrême (le calcul précis avec des modèles plus réalistes sera effectué par le simulateur). Cette phase essentielle est la seule méthode pour vérifier

Fig. 19 – Analyse temporelle d'une porte NAND.

que le fichier-circuit ne comporte pas d'erreur de connexion ou que le circuit étudié est fonctionnellement correct.

- Avant de faire appel à des modèles de composant très raffinés pour simuler un circuit, effectuer préalablement une simulation avec des modèles génériques simplifiés ou même des modèles comportementaux. Cette phase permet d'évaluer le comportement fonctionnel du circuit c'est-à-dire son aptitude à remplir la fonction pour laquelle il a été conçu. La plupart des modèles de bibliothèque ne sont que des modèles génériques auxquels ont été adjoints des limitations dues à la réalisation physique du composant ou des éléments parasites. Si une modélisation comportementale ne conduit pas au résultat escompté il y a peu de chance de l'atteindre avec des modèles plus sophistiqués.

- Dans un petit nombre de cas, il se peut que des modèles comportementaux trop « idéaux » comportant des gains trop importants, ou des impédances trop grandes ou trop petites, ou des discontinuités trop sévères, entraînent des problèmes de convergence de calcul. Le simulateur arrête alors le calcul et émet un message d'erreur. La documentation propose généralement des solutions pour résoudre le problème soit par des modifications de la valeur des paramètres des composants soit par des ajustements des options de calcul.

- Lorsqu'un circuit comporte un grand nombre de composants, il est généralement constitué de plusieurs sous-systèmes réalisant des fonctions électroniques simples. Avant de simuler le circuit complet il est recommandé de tester séparément les différentes parties, cette précaution permet de localiser plus facilement d'éventuels dysfonctionnements et de gagner du temps.

- Avant de lancer une simulation, vérifier que les paramètres de l'analyse ne vont pas produire une quantité colossale de données. Une simulation temporelle de 1 s avec un pas de 10 ns d'un circuit comportant 10 nœuds produira un milliard de valeurs rien que pour les tensions nodales!

Observer que même lorsqu'aucun paramètre de modèle n'est indiqué dans le fichiercircuit, le simulateur utilise des valeurs par défaut qui lui permettent d'effectuer un calcul « réaliste ». Les valeurs par défaut sont précisées dans la documentation.

Tableau II – Identificateurs des composants.

| Ta | <b>Tableau II</b> – Identificateurs des composants. |  |  |

|----|-----------------------------------------------------|--|--|

|    | COMPOSANTS PASSIFS                                  |  |  |

| C  | Condensateur                                        |  |  |

| K  | Mutuelle inductance                                 |  |  |

| L  | Inductance                                          |  |  |

| R  | Résistance                                          |  |  |

|    | COMPOSANTS ACTIFS                                   |  |  |

| D  | Diode                                               |  |  |

| J  | Transistor à effet de champ                         |  |  |

| М  | Transistor MOS                                      |  |  |

| Q  | Transistor bipolaire                                |  |  |

| В  | Transistor MESFET                                   |  |  |

|    | SOURCES INDÉPENDANTES                               |  |  |

| I  | Source indépendante de courant                      |  |  |

| V  | Source indépendante de tension                      |  |  |

|    | SOURCES COMMANDÉES                                  |  |  |

| Е  | Source de tension commandée en tension              |  |  |

| F  | Source de courant commandée en courant              |  |  |

| G  | Source de courant commandée en tension              |  |  |

| Н  | Source de tension commandée en courant              |  |  |

|    | INTERRUPTEURS COMMANDÉS                             |  |  |

| S  | Interrupteur commandé en tension                    |  |  |

| W  | Interrupteur commandé en courant                    |  |  |

|    | AUTRES COMPOSANTS                                   |  |  |

| T  | Ligne de transmission                               |  |  |

| Х  | Sous-circuit                                        |  |  |

Tableau III – Types des modèles de SPICE.

| Type    | Composant | Nature                                   |

|---------|-----------|------------------------------------------|

| CAP     | С         | Condensateur                             |

| IND     | L         | Inductance                               |

| RES     | R         | Résistance                               |

| D       | D         | Diode                                    |

| NPN     | Q         | Transistor bipolaire NPN                 |

| PNP     | Q         | Transistor bipolaire PNP                 |

| LPNP    | Q         | Transistor PNP latéral                   |

| NJF     | J         | FET à jonction canal N                   |

| PJF     | J         | FET à jonction canal P                   |

| NMOS    | М         | MOSFET canal N                           |

| PMOS    | М         | MOSFET canal P                           |

| GASFET  | В         | MESFET AsGa canal N                      |

| CORE    | K         | Noyau magnétique non linéaire (transfo.) |

| VSWITCH | S         | Interrupteur commandé en tension         |

| ISWITCH | W         | Interrupteur commandé en courant         |

| TRN     | T         | Ligne de transmission à pertes           |

Tableau IV – Commandes d'analyse de PSpice.

|        | Tabledd IV Communaes a antaigec ac I Spice.                 |  |  |

|--------|-------------------------------------------------------------|--|--|

| ANALYS | ANALYSES EN CONTINU (NON LINÉAIRES, INDÉPENDANTES DU TEMPS) |  |  |

| .DC    | Calcul de polarisation                                      |  |  |

| .OP    | Édition des résultats d'un calcul de polarisation           |  |  |

| .SENS  | Calcul de sensibilité                                       |  |  |

| .TF    | Fonction de transfert en continu                            |  |  |

| ANALYS | SES DYNAMIQUES (LINÉAIRES, FONCTIONS DE LA FRÉQUENCE)       |  |  |

| . AC   | Analyse en petits signaux                                   |  |  |

| .NOISE | Analyse du bruit                                            |  |  |

| ANAL   | ANALYSES TEMPORELLES (NON LINÉAIRES FONCTIONS DU TEMPS)     |  |  |

| .TRAN  | Réponse temporelle                                          |  |  |

| .FOUR  | Transformée de Fourier                                      |  |  |

|        | ANALYSES MULTIPLES                                          |  |  |

| .STEP  | Paramétrique                                                |  |  |

| .TEMP  | Température                                                 |  |  |

|        | ANALYSES STATISTIQUES (DC, AC OU TRAN)                      |  |  |

| .MC    | Monte Carlo                                                 |  |  |

| .WCASE | Analyse de pire cas                                         |  |  |

|        |                                                             |  |  |

Tableau V – Commandes de contrôle de PSnice.

|           | CONDITIONS INITIALES                                             |  |  |

|-----------|------------------------------------------------------------------|--|--|

| .IC       | .IC Fixe la tension de nœud pour le calcul de polarisation       |  |  |

| . NODESET | Suggère la tension de nœud pour le calcul de polarisation        |  |  |

|           | MODÉLISATION DES COMPOSANTS                                      |  |  |

| .ENDS     | Fin de sous-circuit                                              |  |  |

| .MODEL    | Description d'un modèle de composant                             |  |  |

| .SUBCKT   | Début de sous-circuit                                            |  |  |

|           | ÉDITION DES RÉSULTATS                                            |  |  |

| .PLOT     | Tracé en mode texte                                              |  |  |

| .PRINT    | Édition dans le fichier de sortie                                |  |  |

| .PROBE    | Création du fichier de données pour le post processeur graphique |  |  |

|           | GESTION DES FICHIERS                                             |  |  |

| .END      | Marque la fin du fichier-circuit                                 |  |  |

| .INC      | Inclusion d'un fichier                                           |  |  |

| .LIB      | Référence à une bibliothèque                                     |  |  |

| .PARAM    | Définition de paramètre                                          |  |  |

|           | OPTIONS                                                          |  |  |

| .OPTIONS  | Fixe différentes limites, paramètres de commande et d'édition    |  |  |

| Tableau VI – Format des variables de sortie.                                     |                                                           |  |  |  |

|----------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| ANALYSES .DC ET .TRAN                                                            |                                                           |  |  |  |

| <nom> peut être un composant dipolaire (C, D,E, F, G, H, I, L, R, S, V, W)</nom> |                                                           |  |  |  |

|                                                                                  | ou tripolaire (B, J, M, Q, T, Z)                          |  |  |  |

| I(< nom >)                                                                       | Courant dans un composant dipolaire                       |  |  |  |

| Ix(< nom >)                                                                      | Courant entrant dans une borne d'un tripôle,              |  |  |  |

|                                                                                  | x peut prendre les valeurs suivantes :                    |  |  |  |

|                                                                                  | B (MESFET AsGa) D, G, S                                   |  |  |  |

|                                                                                  | J (FET à jonction) D, G, S                                |  |  |  |

|                                                                                  | M (MOSFET) D, G, S, B                                     |  |  |  |

|                                                                                  | Q (Transistor bipolaire) C, B, E, S                       |  |  |  |

|                                                                                  | T (Ligne de transmission) A, B                            |  |  |  |

|                                                                                  | Z (IGBT) C, G, E                                          |  |  |  |

| $V(\langle næud \rangle)$                                                        | Tension en un nœud                                        |  |  |  |

| $V(\langle n+, n- \rangle)$                                                      | Tension entre deux nœuds                                  |  |  |  |

| V( <nom>)</nom>                                                                  | Tension aux bornes d'un composant dipolaire               |  |  |  |

| $\forall x (< nom >)$                                                            | Tension à une borne d'un composant tripolaire (cf. $Ix$ ) |  |  |  |

| $\forall xy (< nom >)$                                                           | Tension entre deux bornes d'un composant tripolaire       |  |  |  |

|                                                                                  | (y  prend les mêmes valeurs que  x)                       |  |  |  |

|                                                                                  | ANALYSE . AC                                              |  |  |  |

|                                                                                  | Les variables, analogues aux précédentes,                 |  |  |  |

| peuvent ê                                                                        | tre précisées en ajoutant l'un des suffixes suivants :    |  |  |  |

| M (ou rien)                                                                      | Amplitude                                                 |  |  |  |

| P                                                                                | Phase                                                     |  |  |  |

| DB                                                                               | Amplitude en dB                                           |  |  |  |

| R                                                                                | Partie réelle                                             |  |  |  |

| I                                                                                | Partie imaginaire                                         |  |  |  |

| G                                                                                | Temps de groupe $(-d\varphi/df)$                          |  |  |  |

|                                                                                  | ANALYSE DU BRUIT : .NOISE                                 |  |  |  |

| INOISE                                                                           | Somme quadratique du bruit ramené au nœud d'entrée        |  |  |  |

| ONOISE                                                                           | Équivalent de INOISE ramené au nœud de sortie             |  |  |  |

| DB(INOISE)                                                                       | INOISE en dB                                              |  |  |  |

| DB(ONOISE)                                                                       | ONOISE en dB                                              |  |  |  |

Tableau VII – Exemples de formats des variables de sortie.

|                | EXEMPLES (.DC, .TRAN)                                |  |

|----------------|------------------------------------------------------|--|

| I(D5)          | Courant dans la diode D5                             |  |

| IG(J10)        | Courant entrant dans la grille de J10                |  |

| V(3)           | Tension entre le nœud 3 et la masse                  |  |

| V(3,2)         | Tension entre le nœud 3 et le nœud 2                 |  |

| V(R1)          | Tension aux bornes de la résistance R1               |  |

| VB(Q3)         | Tension entre la base de Q3 et la masse              |  |

| VGS(M13)       | Tension grille-source de M13                         |  |

| EXEMPLES (.AC) |                                                      |  |

| II(R13)        | Partie imaginaire du courant dans R13                |  |

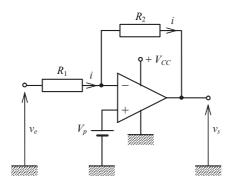

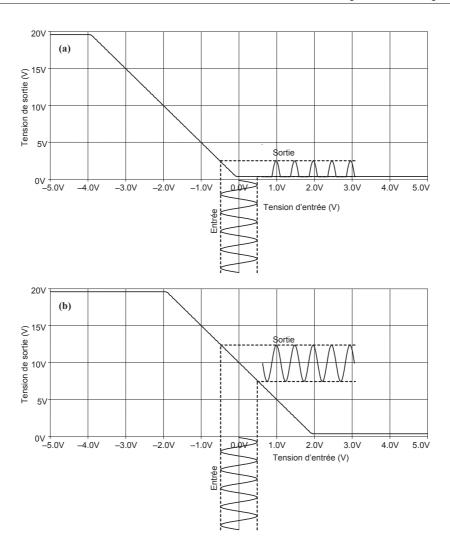

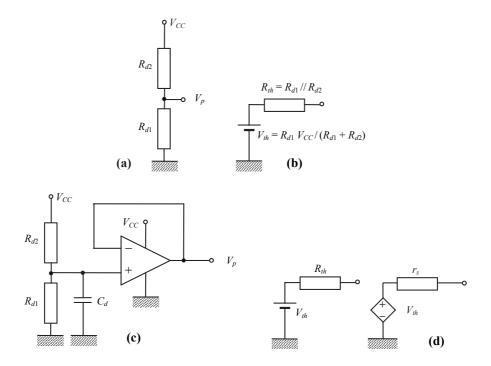

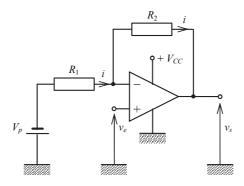

| IGG(M3)        | Temps de groupe du courant de grille de M3           |  |