## INTRODUCTION

## 1 Définition d'un microprocesseur

On peut donner du terme microprocesseur la définition suivante : "Composant renfermant dans un seul boîtier l'unité de contrôle et l'unité de traitement d'une machine informatique de type VON NEUMANN"

Cette définition exclut volontairement :

- Les composants en plusieurs boîtiers (micros en tranches)

- Les architectures non VON NEUMANN (GAPP, Transputers)

- Les microcontrôleurs qui incluent d'autres composantes des systèmes informatiques (mémoire, entrées/sorties)

La vocation de ces composants est de constituer l'unité centrale de micro-ordinateurs et, à l'heure actuelle, de mini-ordinateurs. Toutefois leur prix raisonnable et leurs performances permettent leur utilisation dans des systèmes informatiques dédiés (concentrateurs de lignes, noeuds de réseaux, pilotes de robots etc).

#### 2 Historique

L'histoire des microprocesseurs est intimement liée à celle de la technologie des semi-conducteurs dont voici les principales étapes :

- 1940 Invention du transistor

- 1950 Jack Saint CLAIR (TEXAS INSTRUMENTS) produit le ler circuit intégré (CI)

- 1961 Début de la production en série des CI

- 1964 Intégration à petite échelle (SSI de 1 à 10 transistors)

- 1968 Intégration à moyenne échelle (MSI de 10 à 500 transistors)

- 1971 Intégration à grande échelle (LSI de 500 à 20 000 transistors)

- 1980 Intégration à très grande échelle (VLSI plus de 20 000 transistors)

Le premier microprocesseur a été fabriqué par INTEL en 1971. C'était un 4 bits baptisé 4004 destiné à équiper des calculatrices de bureau.

En 1972 INTEL produit le premier microprocesseur 8 bits baptisé 8008 par référence au précédent. Ce microprocesseur était destiné à répondre à un contrat de fabrication d'un terminal. En réalité le 8008 s'est avéré trop lent pour satisfaire au cahier des charges du terminal et INTEL a décidé de tenter le lancement de ce produit sur le marché grand public.

L'énorme succès de cette initiative fut à l'origine de la fabrication massive des microprocesseurs.

A la suite du succès du 8008, INTEL produisit dès 1974 le 8080 qui constituera le premier élément de la future famille de microprocesseurs de ce fabriquant.

En 1974, MOTOROLA, autre fondeur de silicium, décide de lancer le 6800 qui constituera lui aussi le début d'une grande famille.

Les années 70 voient alors apparaître de petites entreprises de fabrication de microprocesseurs souvent constituées par des transfuges des deux grandes compagnies.

On peut notamment citer MOSTEK avec son 6502 très inspiré du 6800 et ZILOG avec son Z80 qui constitue une amélioration technique du 8080 (augmentation du nombre de registres, simplification de l'alimentation...)

Les autres grands constructeurs (TEXAS INSTRUMENT, FAIRCHILD , RCA , SIGNETICS etc) hésitent encore à se lancer dans ce marché.

Ces composants seront à la base des premiers micro-ordinateurs tant personnels (TANDY avec son TRS80 muni d'un Z80 et le tout premier APPLE avec un 6502) que professionnels (EXORCISER de MOTOROLA et multiples constructeurs développant autours du format de carte S100 pour 8080 et Z80).

On peut remarquer que la conception même du composant avait été chez MOTOROLA plus guidée par des considérations informatiques qu'électroniques (possibilité de tests selon la représentation des nombres, sauvegarde automatique de contexte, distinction entre interruption matérielle et logicielle...). Tandis qu'INTEL et ZILOG avaient opté pour une approche plus matérielle (test de parité, pas de sauvegarde automatique de contexte pour prendre en compte les interruptions plus rapidement, rafraîchissement de mémoires dynamiques).

Paradoxalement la famille des 8 bits d'INTEL a bénéficié d'un grand effort de développement logiciel (écriture des systèmes d'exploitation CPM puis MPM et CCPM) alors que la famille MOTOROLA se voyait attribuer des systèmes d'exploitation plus "maison" et moins aptes à accueillir des progiciels.

Très vite les 8 bits commencent à atteindre la limite de leurs performances et les constructeurs se penchent sur de nouvelles solutions.

Les principaux reproches faits aux 8 bits sont :

- peu d'espace mémoire accessible (64K octets)

- peu de types d'informations manipulés (1 ou 2 octets)

- pas adaptés aux architectures multi-processeurs

- peu de modes d'adressage

Pour toutes ces raisons les constructeurs commencent à étudier une nouvelle génération de microprocesseurs. De sorte que l'on verra apparaître des microprocesseurs 8 bits plus puissants permettant de manipuler plus facilement des informations sur 16 bits et offrant de nouvelles possibilités d'adressage comme le 6809 de MOTOROLA ou le 8085 d'INTEL.

L'utilisation de plus en plus "informatique" des microprocesseurs (langages évolués , systèmes d'exploitation performants) a rapidement attiré les constructeurs vers des produits plus proches des unités centrales d'ordinateurs.

L'année 78 a vu donc apparaître sur le marché des microprocesseurs 16 bits offrant une capacité d'adressage de mémoire d'au moins lM octets (2<sup>20</sup>), des performances plusieurs fois supérieures à celles des 8 bits, un large éventail de modes d'adressage (segments, bases, adresses relatives et, plus tard, mémoire virtuelle) et des possibilités plus importantes de manipulation de données (bit, chaîne de caractères, mots de 8, 16, 32 bits, quantités numériques en ASCII et en DCB...).

Force est de constater que l'idée première du petit composant à tout faire a fait place au microprocesseur unité centrale d'ordinateur.

Les deux grands constructeurs INTEL et MOTOROLA ont alors proposé les éléments de leur nouvelle génération de microprocesseurs.

# LES ANCÊTRES

Les microprocesseurs 4 et 8 bits font déjà partie du passé. Ils illustrent malgré tout les principes de fonctionnement de ce type de composants. Nous nous contenterons d'un petit tour d'horizon sous la forme des tableaux ci-après et de l'étude d'un microprocesseur de la 1<sup>ère</sup> génération le 6800 de MOTOROLA.

## 1 Les 4 bits

| Constructeur<br>Référence         | INTEL<br>4004 | INTEL<br>4040 | ROCKWELL<br>PPS4 | FAIRCHILD<br>PPS25 | TEXAS INS<br>TMS 1000 |

|-----------------------------------|---------------|---------------|------------------|--------------------|-----------------------|

| Nbre d'instr                      | 46            | 60            | 50               | 95                 | petit                 |

| Temps d'addition entre regs en ms | 8             | 8             | 5                | 3                  | 15                    |

| Espace mémoire                    | 4K            | 8K            | 4K               | 6,5K               | 1K                    |

| Registres d'usage<br>général      | 16            | 24            | 4                | 1                  | 4                     |

Le 4004, apparu en 1970, intègre 2250 transistors. Il gère les appels de sous programmes par une pile interne à 4 niveaux.

Le 4040, datant de 1972, ajoute 4 niveaux à cette pile ainsi que la gestion des interruptions.

## 2 Les 8 bits

| Constructeur<br>Référence         | INTEL<br>8008 | INTEL INTEL 8080 8085 |             | MOTOROLA<br>6800 |

|-----------------------------------|---------------|-----------------------|-------------|------------------|

| Nbre d'instr                      | 48            | 69                    | 69 71       |                  |

| Temps d'addition entre regs en ms | 12,5 à 20     | 1,3 à 2               | 1,3 à 2 1,3 |                  |

| Espace mémoire                    | 16K           | 64K                   | 64K         | 64K              |

| Registres d'usage<br>général      | 7             | 7                     | 7           | 3                |

| Nombre de transistors             | 3300          | 4000                  | 6200        |                  |

| Horloge en MHz                    | 0,3           | 2 2,67 ou 3,125       | 3,5 ou 6    | 1 1,5 ou 2       |

| Année                             | 1972          | 1974                  | 1976        | 1974             |

| Constructeur<br>Référence            | ZILOG<br>Z80 | MOSTEK<br>6502 | ROCKWELL<br>PPS8 | NATIONAL<br>SC/MP     |

|--------------------------------------|--------------|----------------|------------------|-----------------------|

| Nbre d'instr                         | 69           | 71             | 90               | 50                    |

| Temps d'addition<br>entre regs en ms | 1,6          | 2              | 4                | 5 à 25                |

| Espace mémoire                       | 64K          | 64K            | 32K              | 64K en pages de<br>4K |

| Regs généraux                        | 17           | 3              | 3                | 6                     |

| Année                                | 1976         | 1975           |                  | 1976                  |

L'architecture interne de ces microprocesseurs est très simple et directement calquée sur la structure VON NEUMANN. Nous nous contenterons d'analyser la structure de l'un d'entre eux.

## 3 Un exemple le 6800

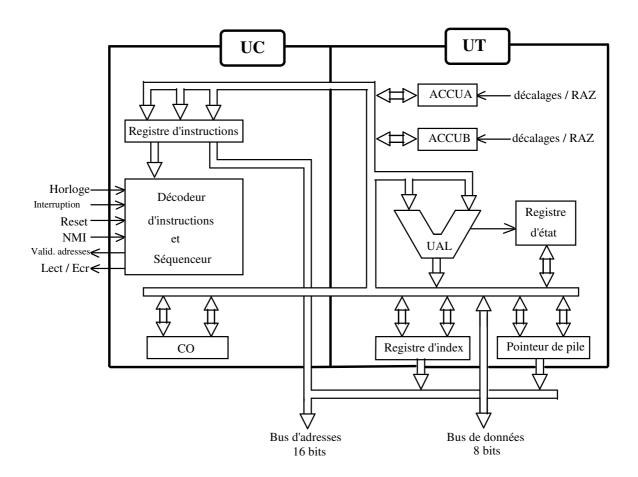

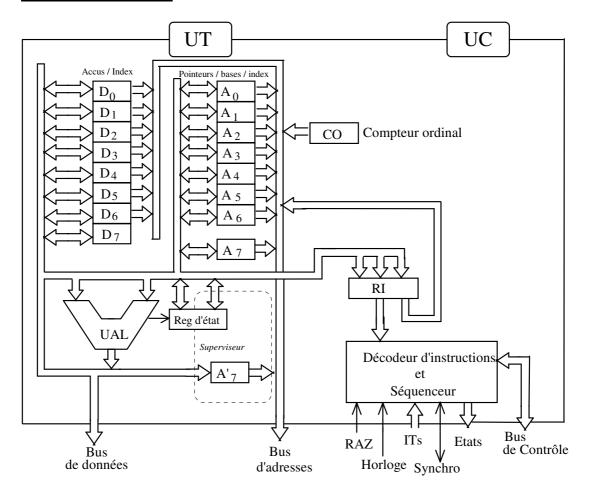

## 3.1 Architecture interne

### 3.2 Les registres

Le **compteur ordinal** (CO) sur 16 bits pointe sur l'instruction à traiter.

Le **pointeur de pile** (SP) sur 16 bits contient l'adresse du sommet de pile. Cette pile peut être placée n'importe où en mémoire.

Elle est utilisée de façon automatique pour sauvegarder l'adresse de retour lors de l'appel de sous programmes et pour sauvegarder le contexte (l'ensemble des registres) lors de la prise en compte d'une interruption.

Elle peut aussi être utilisée pour des sauvegardes temporaires ou des passages de paramètres grâce à des instructions spéciales (PUSH et PULL).

Le **registre d'index** (X) sur 16 bits est utilisé pour l'adressage indexé c'est à dire que l'adresse de l'opérande est obtenue en faisant la somme du contenu de ce registre avec un déplacement fixe placé dans l'instruction.

Les **accumulateurs** (A et B) sur 8 bits, ils servent d'opérandes à l'UAL et en réceptionnent les résultats. Ils permettent les opérations arithmétiques d'addition, de soustraction, d'incrémentation, de décrémentation et de changement de signe ainsi que les décalages et les opérations logiques (ET, OU, OU Exclusif, NON).

Le **registre de code de conditions** sur 8 bits contient les indicateurs de l'UAL (signe, résultat nul, débordement, retenue) ainsi qu'un bit indiquant si les interruptions doivent ou pas être prises en compte (masque d'interruptions).

## 3.3 Les opérandes

Le 6800 traite les opérandes sur 8 bits suivants :

- Entiers naturels (0 à 255)

- Entiers relatifs en représentation complément à 2 (-127 à 127)

- Décimaux en DCB sur 2 chiffres (8 bits)

Les opérandes sur 16 bits ne peuvent être traités que par "tranches" successives de 8 bits.

On peut toutefois noter que l'index X (sur 16 bits) peut subir des transferts vers et depuis 2 octets consécutifs en mémoire ainsi que des incrémentations, des décrémentations et des comparaisons d'égalité avec un mot constitué de 2 octets consécutifs en mémoire.

#### 3.4 Les instructions

On peut les découper en 7 groupes :

#### - Arithmétiques

- Addition ADD et ADC <sup>1</sup>

- Soustraction SUB et SBC <sup>1</sup>

Mise à zéro CLR

Changement de signe NEG

Incrémentation INC

- Décrémentation DEC

- Ajustement décimal DAA

Chacune de ces opérations peut porter sur l'un ou l'autre des accumulateurs (A ou B) ainsi que sur un opérande en mémoire à l'exception de l'ajustement décimal qui ne peut être effectué que sur l'accu A.

## - Logiques

- Test de bit BIT<sup>2</sup>

<sup>&</sup>lt;sup>1</sup>Il existe outre les additions et soustractions habituelles (ADD et SUB) deux opérations (ADC et SBC) permettant de traiter le report de retenue lors de l'utilisation d'opérandes par "tranches" de 8 bits.

Test de signe

Comparaison

Non

Ou

Et

Ou exclusif

EOR

Ces opérations, à l'exception de COM et TST qui peuvent traiter des opérandes en mémoire, ne peuvent porter que sur les accumulateurs A et B.

#### - Transferts

| - Chargement d'un accu  | LDAA        | LDAB        |

|-------------------------|-------------|-------------|

| - Rangement d'un accu   | STAA        | STAB        |

| - Empilement d'un accu  | <b>PSHA</b> | <b>PSHB</b> |

| - Dépilement d'un accu  | <b>PULA</b> | <b>PULB</b> |

| - Transfert entre accus | TBA         | TAB         |

#### - Décalages

| - Logique à droite et à gauche      | LSR | LSL        |

|-------------------------------------|-----|------------|

| - Arithmétique à droite et à gauche | ASR | <b>ASL</b> |

| - Circulaire à droite et à gauche   | ROR | ROL        |

Chacune de ces opérations peut porter sur l'un des accus ainsi que sur un opérande en mémoire.

### - Opérations sur l'index et le pointeur de pile

| - Incrémentation | INX   | INS              |

|------------------|-------|------------------|

| - Décrémentation | DEX   | DES              |

| - Chargement     | LDX   | LDS <sup>3</sup> |

| - Rangement      | STX   | STS <sup>2</sup> |

| - Transferts     | TXS   | TSX 4            |

| - Comparaison    | CPX 5 |                  |

## - Ruptures de séquence

| - Branchements | inconditionnels | BRA | IMP |

|----------------|-----------------|-----|-----|

- Branchements conditionnels :

si égal

$\begin{array}{lll} \text{si différent} & \text{BNE} \\ \text{si < } & \text{BCS entre entiers naturels} & \text{BLT entre relatifs} \\ \text{si < ou} = & \text{BLS entre entiers naturels} & \text{BLE entre relatifs} \\ \text{si > } & \text{BHI entre entiers naturels} & \text{BGT entre relatifs} \\ \text{si > ou} = & \text{BCC entre entiers naturels} & \text{BGE entre relatifs} \\ \end{array}$

**BEQ**

si débordement BVS

<sup>&</sup>lt;sup>2</sup> BIT est un ET logique sans production de résultat CMP est une soustraction sans production de résultat TST se contente d'une comparaison à O (nul , signe) Ces instructions permettent de positionner les indicateurs du registre de code de conditions utilisés lors des ruptures de séquence conditionnelles (branchements conditionnells).

<sup>&</sup>lt;sup>3</sup> Le chargement et le rangement en mémoire s'effectuent sur 2 octets consécutifs de la façon suivante : écriture / lecture de l'octet de fort poids à l'adresse désignée comme opérande puis écriture / lecture de l'octet de faible poids à l'adresse suivante.

<sup>&</sup>lt;sup>4</sup> Le transfert entre X et SP n'est pas direct mais tient compte du fait que SP désigne le sommet de pile sous la forme de la première place disponible et non de la dernière occupée ainsi : TSX transfère SP+l dans X et TXS transfère X-l dans SP.

<sup>&</sup>lt;sup>5</sup> La comparaison n'existe pas sur SP et celle qui existe sur X ne permet que de tester l'égalité.

| si non débordement                | BVC              |     |

|-----------------------------------|------------------|-----|

| si positif                        | BPL              |     |

| si négatif                        | BMI              |     |

|                                   |                  |     |

| - Appel de sous programme         | BSR              | JSR |

| - Retour de sous programme        | RTS              |     |

| - Appel d'interruption logicielle | SWI <sup>6</sup> |     |

| - Retour d'interruption           | RTI              |     |

#### - Opérations sur le registre code condition

- Attente d'interruption

| - Mise à 0/1 de la retenue              | CLC | SEC |

|-----------------------------------------|-----|-----|

| - Mise à 0/1 du débordement             | CLV | SEV |

| - Masquage/démasquage des interruptions | SEI | CLI |

| - Transferts avec l'accu A              | TAP | TPA |

WAI $^7$

## 3.5 La mémoire et l'adressage

Le bus d'adresses est de 16 bits donc l'espace mémoire ne peut dépasser 64K octets. Le 6800 possède les modes d'adressage suivants :

- inhérent : L'instruction n'a pas d'opérande (RTS) ou bien l'opérande est dans un registre (CLRA)

- **immédiat** : La valeur de l'opérande est dans l'instruction (ex : ADDA #3 qui ajoute 3 à l'accumulateur A)

- **direct et étendu** : L'opérande est désigné par son adresse en mémoire soit sur 8 bits (direct) soit sur 16 bits (étendu).

- indexé: L'opérande est désigné par une adresse obtenue par addition du contenu du registre d'index X et de la valeur placée dans l'instruction. Le déplacement est fixe et constitué d'un entier naturel sur 8 bits  $(0 \ à \ 255)$ .

- **relatif**: Ce mode d'adressage est réservé aux instructions de rupture de séquence. L'instruction contient un déplacement fixe constitué d'un entier relatif sur 8 bits qui sera ajouté au contenu du compteur ordinal (CO) pour calculer l'adresse de la prochaine instruction. Le déplacement ne peut dépasser les limites de + à -127.

#### 3.6 Quelques remarques

#### 1°) L'Horloge

L'horloge de séquencement du 6800 est de lMHz (des modèles ultérieurs 68A00 et 68B00 supportent des horloges de 1,5 et 2MHz).

Toute instruction dure au moins 2 périodes d'horloge et aucune ne dépasse 12 périodes (la plus grande partie des instructions se situant entre 2 et 6 périodes).

Contrairement aux microprocesseurs d'INTEL et ZILOG le fonctionnement du 6800 est biphasé c'est à dire que pendant la l<sup>ère</sup> moitié de la période d'horloge s'effectuent les opérations internes (décodage de l'instruction,

IRQ qui peut être masquée par un bit du registre de code de conditions NMI qui ne peut pas être ignorée et une interruption logicielle : SWI

<sup>&</sup>lt;sup>6</sup> Le 6800 possède 2 lignes d'interruptions matérielles :

<sup>&</sup>lt;sup>7</sup>L'instruction WAI provoque l'arrêt du processeur jusqu'à ce qu'arrive une interruption physique.

UAL, transferts de registres) et pendant la 2<sup>ème</sup> moitié les échanges avec la mémoire. Le fonctionnement est totalement synchrone c'est à dire que la mémoire doit pouvoir "répondre" pendant la demi-période qui lui est allouée et il n'existe aucun moyen simple de faire attendre le microprocesseur si la mémoire est trop lente.

## 2°) Les Entrés/Sorties

Le 6800 ne possède aucune instruction spécifique d'entrée/sortie (contrairement aux 8080 et Z80 qui ont des instructions IN et OUT). Les registres des contrôleurs de périphériques apparaissent comme des zones de mémoire classiques et peuvent être traités comme des opérandes par toutes les instructions.

## LES MICROPROCESSEURS ACTUELS

### 1 Présentation générale

La génération actuelle de microprocesseurs a su tirer les leçons des problèmes rencontrés par les utilisateurs de 8 bits entre 1974 et 1980. On peut dégager deux grands axes d'évolution des microprocesseurs :

#### **Evolution logicielle**

Les nouveaux microprocesseurs sont dotés d'instructions et surtout de modes d'adressage permettant l'utilisation de langages évolués et la réalisation de systèmes d'exploitation multitâches modernes :

- Instructions permettant le passage de paramètres

- Instructions permettant la manipulation de données complexes ( tableaux, chaînes de caractères...)

- Mémoire virtuelle

- Niveaux de privilèges et protection

- Adressage de mémoire par base, segments, index avec ou sans indirection

- Instructions de changement de tâche

#### Evolution matérielle

Le degré d'intégration plus élevé permet d'avoir plus de registres et des unités de traitement plus puissantes. Cependant la principale évolution technique concerne la vitesse de traitement :

- Technologies rapides permettant des horloges dépassant les 100 MHz

- Parallélisme de fonctionnement

- Intégration des antémémoires

- Prédiction d'instructions

- Gestion de co-processeurs et de multi-processeurs

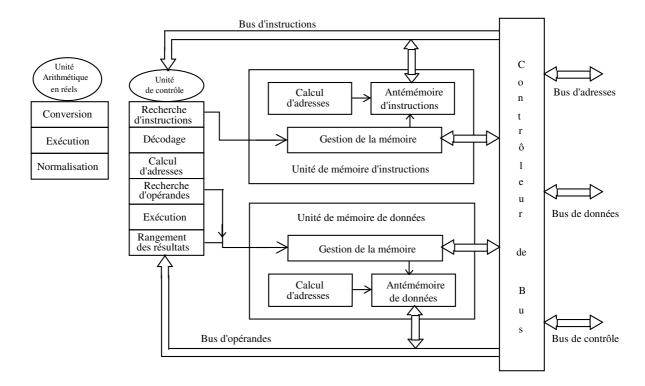

La période 1978-1993 se caractérise par une mise à profit des progrès des technologies des circuits intégrés (technologie CISC<sup>8</sup>) tandis que la période suivante met en évidence la nécessité de remettre en question des principes même de ces processeurs (technologie RISC<sup>9</sup>).

Nous allons maintenant essayer de décrire les membres des deux grandes familles de microprocesseurs de la nouvelle génération qui se partagent à l'heure actuelle le marché (INTEL et MOTOROLA).

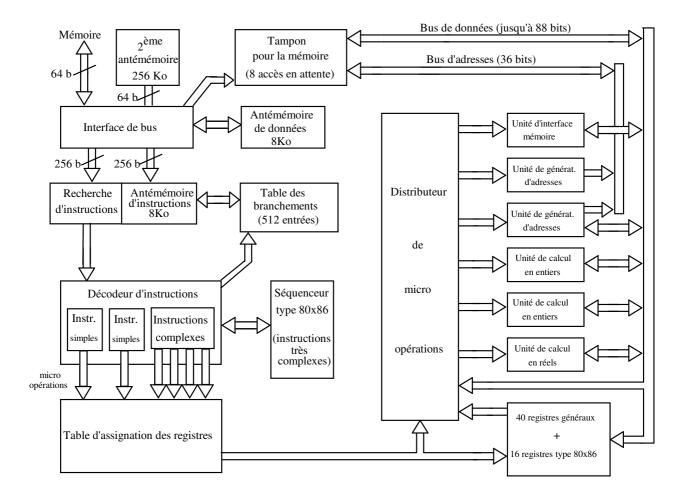

Dans un premier temps, INTEL proposera les successeurs du 8080 : 8086, 80286, 80386, 80486 et Pentium qui sont une évolution logique du 8080 (passage à 16 puis 32 bits, gestion de mémoire virtuelle et paginée, intégration d'antémémoires, mise en place de protections et d'une arthmétique réelle) puis, l'apparition du P6, constitue un passage à la technologie RISC rendu difficile par la nécessité de conserver la compatibilité au niveau du code avec les processeurs antérieurs. INTEL sera donc conduit, à partir de cette époque à intégrer un compilateur permettant la traduction des instructions de type 80x86 en instructions RISC exécutées par le processeur. De plus INTEL introduira des instructions issues des processeurs de signal (DSP) de façon à accélérer les traitements d'image et de sons imposés par les environnements multimédia.

MOTOROLA connaîtra le même type d'évolution issue du 6800 : 68000, 68010, 68020, 68030, 68040 et 68060 (passage à 16 puis à 32 bits, gestion de mémoire virtuelle et paginée, intégration d'antémémoires,

Les Microprocesseurs

M. DALMAU, IUT de Bayonne

<sup>&</sup>lt;sup>8</sup> CISC Complex Instruction Set Computer, processeur doté d'un jeu d'instructions complexes tentant de se rapprocher des instructions des langages évolués.

<sup>&</sup>lt;sup>9</sup> RISC Reduced Instruction Set Computer processeur à jeu d'instruction réduit. On cherche à réaliser des instructions simples pouvant être exécutées très rapidement et se prètant facilement à une exécution en parallèle ou en pipe line.

mise en place de protections et d'une arthmétique réelle) puis, la définition de la famille Power PC, constitue un passage à la technologie RISC sans souci de compatibilité avec les processeurs antérieurs. Cette rupture de compatibilité donnera, au début, à MOTOROLA une avance sensible en terme de performance.

#### 2 La famille INTEL

Elle est constituée de 6 generations :

- Le 8086 avec sa version 8 bits le 8088 et son "grand frère" le 80186 ayant lui aussi sa version 8 bits le 80188

- Le 80286 qui ajoute au 8086 une gestion de mémoire virtuelle et de tâches

- Le 80386 le premier 32 bits de la famille possédant aussi une gestion de mémoire virtuelle et de tâches

- le 80486 qui ajoute au 80386 une arithmétique réelle intégrée et un contrôleur d'antémémoire.

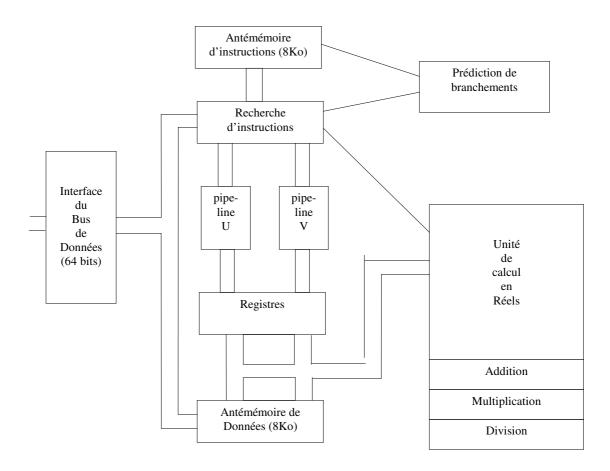

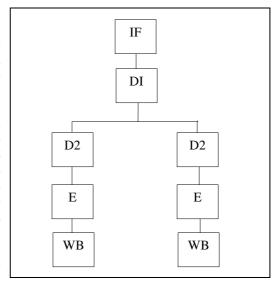

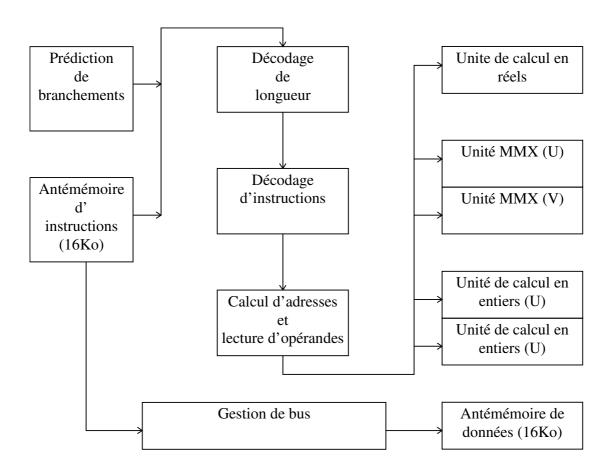

- Le P5 (Pentium) qui ajoute au 80486 un traitement en parallèle de certaines instructions.

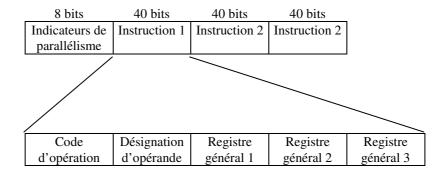

- Le P6 (Pentium Pro) est un processeur RISC doté d'un compilateur câblé pour transformer les instructions de type 80x86 en instructions RISC. Le Klamath ou Pentium II connu selon les modèles sous plusieurs appellations (Deschutes, Celeron, Xeon, Katmai ...).

Des versions MMX, c'est à dire intégrant des instructions de type traitement de signal, des processeurs P5 et P6 sont proposées à partir de 1997 (Tillamook).

Les générations futures (Merced puis McKinley) de processeurs 64 bits devraient apparaître à l'horizon 2000 en collaboration avec HP (architecture IA-64).

Le tableau suivant établit une comparaison entre les principaux éléments de cette famille :

| Modèle                | 8086   | 80286   | 80386   | 80486            | Pentium (P5)     | Pentium<br>Pro (P6) | Pentium<br>II |

|-----------------------|--------|---------|---------|------------------|------------------|---------------------|---------------|

| Année                 | 1978   | 1982    | 1985    | 1989             | 1993             | 1995                | 1997          |

| Nbre de transistors   | 29 000 | 134 000 | 275 000 | 1,2 M à<br>1,6 M | 3,1 M à<br>4,4 M | 5,5 M               | 7,5 M         |

| Performance           | 0,3    | 1,2     | 5 à 10  | 20 à 50          | 80 à 280         | 250 à 350           | 380 à 510     |

| Unités<br>d'exécution | 1      | 1       | 1       | 1                | 3                | 5                   | 5             |

Cependant, à l'intérieur de ces grands types sont apparus des quantités importantes de variantes (surtout pour les 80386 et 80486). Le tableau suivant tente de situer la plupart de ces processeurs :

# Les principaux éléments de la famille INTEL et compatibles

| Processeur              | Horloge (MHz)                                    | Bus de<br>données | Données<br>internes | Bus d'<br>adresses | Adresse<br>virtuelle | Anté-mémoire                  | Arith.<br>réelle |

|-------------------------|--------------------------------------------------|-------------------|---------------------|--------------------|----------------------|-------------------------------|------------------|

| 8086                    | 4 5 8 10 12                                      | 16 bits           | 16 bits             | 20 bits            | Non                  | Non                           | Ext.             |

| 80286                   | 6 8 10 12 16 20 25                               | 16                | 16                  | 24                 | 30 bits              | Non                           | Ext.             |

| 80386 SX                | 16 20 25 33 40                                   | 16                | 32                  | 24                 | 46                   | Non                           | Ext.             |

| 80386 SL                | 20 25 16 33                                      | 16                | 32                  | 24                 | 46                   | Non                           | Ext.             |

| 80386 SLC               | 16 20 25                                         | 16                | 32                  | 24                 | 46                   | 8K                            | Ext.             |

| 80386 DX                | 12 16 20 25 33 40                                | 32                | 32                  | 32                 | 46                   | Non                           | Ext.             |

| 80486 SLC               | 16 20 25 33 40                                   | 16                | 32                  | 24                 | 46                   | 1 ou 16K                      | Ext.             |

| 80486 SLC/e             | 20 25                                            | 16                | 32                  | 24                 | 46                   | 1K                            | Ext.             |

| 80486 SLC2              | 16/32 <sup>(10)</sup> 20/40 25/50 33/66<br>40/80 | 16                | 32                  | 24                 | 46                   | 16K                           | Ext.             |

| 80486 SL                | 25 33                                            | 32                | 32                  | 32                 | 46                   | 8K                            | Oui              |

| 80486 DLC               | 25 33 40                                         | 32                | 32                  | 32                 | 46                   | 1K ou 16K                     | Ext.             |

| 80486 SX                | 16 20 25 33 40                                   | 32                | 32                  | 32                 | 46                   | 8K                            | Ext.             |

| 80486 SX2               | 25/50 <sup>(1)</sup> 33/66                       | 32                | 32                  | 32                 | 46                   | 8K                            | Ext.             |

| 80486 DX                | 20 25 33 40 50                                   | 32                | 32                  | 32                 | 46                   | 8K                            | Oui              |

| 80486 DX2               | 20/40 <sup>(1)</sup> 25/50 33/66 40/80           | 32                | 32                  | 32                 | 46                   | 8K                            | Oui              |

| 80486DX4                | 25/75 <sup>(1)</sup> 33/99 40/120                | 32                | 32                  | 32                 | 46                   | 8 ou 16K                      | Oui              |

| Am5x86                  | 33/133 40/160                                    | 32                | 32                  | 32                 | 46                   | 16K                           | Oui              |

| Overdrive               | 16/33 <sup>(1)</sup> 20/40 25/50 33/66           | 32                | 32                  | 32                 | 46                   | 8K                            | Oui              |

| Pentium (P5<br>ou P54C) | 60 66 75 90 100 120 133<br>150 166 200           | 64                | 32                  | 32                 | 46                   | 8K (code) +<br>8K (données)   | Oui              |

| Pentium Pro (P6)        | 120 133 150 166 180 200<br>233                   | 64                | 64                  | 32                 | 46                   | 8K + 8K<br>+ 256 ou 512K      | Oui              |

| Pentium<br>MMX (P55)    | 166 200 233 266                                  | 64                | 32                  | 36                 | 46                   | 16K (code) +<br>16K (données) | Oui +<br>MMX     |

| Pentium II              | 233 266 300 350 400                              | 64                | 32                  | 36                 | 46                   | 16K + 16K<br>+512 Ko          | Oui+<br>MMX      |

| Merced                  | 500 1000                                         | 64                | 64                  | 36                 | 46                   | 8K + 8K<br>+ 256K             | Oui +<br>MMX     |

$^{10}$  Ces processeurs divisent par 2 ou 3 leur fréquence d'horloge lors des accès à la mémoire.

#### 3 La famille MOTOROLA

### 1°) La famille des processeurs CISC (famille 680xx)

Elle est constituée de 5 générations :

- Le 68000 le 16 bits et sa version 8 bits le 68008.

- Le 68010 qui ajoute au 68000 des signaux de gestion de mémoire virtuelle et sa version étendue en adressage: le 68012.

- Le 68020 le 32 bits qui, outre les signaux de gestion de mémoire virtuelle, intègre une antémémoire pour les instructions.

- Le 68030 le 32 bits qui, outre les signaux de mémoire virtuelle, intègre un dispositif de pagination ainsi qu'une antémémoire pour les instructions et une autre pour les données.

- Le 68040 qui intègre l'unité de calcul en réels virgule flottante.

- Le 68060 qui parallélise l'exécution de certaines instructions

| TYPE  | HORLOGE<br>(Fréquence) | Cycles<br>UAL/instr | MIPS      | MFLOPS     | 1er<br>échantillon |

|-------|------------------------|---------------------|-----------|------------|--------------------|

| 68000 | 8 - 16,7               | 5,2                 | 0,7 - 1,3 |            | 1979               |

| 68010 | 8 - 12,5               | 5,1                 | 0,8 - 1,2 |            | 1982               |

| 68020 | 12,5 - 33,3            | 3,3                 | 2 - 5,5   | 0,1 - 0,25 | 1984               |

| 68030 | 16,6 - 50              | 2,6                 | 5 - 12    | 0,25 - 0,5 | 1987               |

| 68040 | 25 - 40                | 1,3                 | 19 - 29   | 3,5 - 5,6  | 1989               |

<u>Remarque</u>: Le 6809, souvent considéré comme le premier élément de la nouvelle génération de microprocesseurs de MOTOROLA, n'est en réalité, qu'une évolution du 6800 :

- permettant le traitement d'opérandes sur 16 bits

- possédant un registre d'index supplémentaire et un pointeur de pile de l'utilisateur.

- permettant les adressages indirect et relatif au compteur ordinal ainsi que la pré-décrémentation et la post-incrémentation d'index.

Il est environ 3,5 fois plus performant que le 6800 mais ne constitue tout de même pas un vrai 16 bits (il est plus comparable au 8088 qu'au 8086).

## 2°) La famille des processeurs RISC (famille Power PC)

L'architecture Power PC développée par MOTOROLA et IBM n'assure aucune compatibilité avec les 68xxx. Le choix a été délibérément fait de rompre cette filiation et de réaliser des processeurs RISC.

Toutefois afin que cette étude des principaux microprocesseurs soit le plus complète possible le Power PC sera étudié en fin de ce chapitre.

On y trouve 5 générations de processeurs :

- La première génération est constitué par les MPC 601 et MPC 602.

- La deuxième génération est constituée par les MPC 603, 603e, 604, 604e et 620.

- La troisième génération (G3) en 1998.

- La quatrième génération (G4) en 1999.

- Enfin, la cinquième génération, appelée 2K en 2001.

# Les principaux microprocesseurs MOTOROLA

| Processeur          | Année | Horloge<br>(Mhz)      | Bus de<br>données<br>(bits) | Données<br>internes<br>(bits) | Bus d'<br>adresses<br>(bits) | Adresse virtuelle (bits) | Anté-<br>mémoire<br>(octets) | Arithm.<br>réelle |

|---------------------|-------|-----------------------|-----------------------------|-------------------------------|------------------------------|--------------------------|------------------------------|-------------------|

| 68000               | 1979  | 8 10 12,5<br>16       | 16                          | 32                            | 24                           | Non                      | Non                          | Ext.              |

| 68010               | 1982  | 8 10 12,5             | 16                          | 32                            | 24                           | Non                      | Non                          | Ext.              |

| 68012               |       | 8 10 12,5             | 32                          | 32                            | 30                           | Non                      | Non                          | Ext.              |

| 68020               | 1984  | 12,5 16,7<br>20 25 33 | 32                          | 32                            | 32                           | Non                      | 64                           | Ext.              |

| 68030               | 1987  | 16,7 20 25<br>33 50   | 32                          | 32                            | 32                           | Non                      | 64 + 64                      | Ext.              |

| 68040               | 1989  | 25 33 50              | 32                          | 32                            | 32                           | Non                      | 4K + 4K                      | Oui               |

| 68LC040             | 1991  | 25 33 40              | 32                          | 32                            | 32                           | Non                      | 64 + 64                      | Ext               |

| 68060               | 1994  | 50 66                 | 32                          | 32                            | 32                           | Non                      | 8K + 8K                      | Oui               |

| Power PC 601<br>602 | 1994  | 50 60 66<br>80        | 64                          | 32                            | 32                           | 52                       | 32K                          | Oui               |

| Power PC 603        | 1994  | 50 60 66<br>80        | 64                          | 32                            | 32                           | 52                       | 8K+8K                        | Oui               |

| Power PC 603e       | 1994  | 100 200<br>240        | 64                          | 32                            | 32                           | 52                       | 16K+16K                      | Oui               |

| Power PC 604        | 1995  | 75 100 120<br>133     | 64                          | 32                            | 32                           | 52                       | 16K+16K                      | Oui               |

| Power PC 604e       | 1995  | 75 100 120<br>133     | 64                          | 32                            | 32                           | 52                       | 32K+32K                      | Oui               |

| Power PC<br>620     | 1997  | 80 130 133            | 128                         | 64                            | 40                           | 80                       | 32K+32K                      | Oui               |

| G3                  | 1998  | 250                   | 64                          | 32                            | 32                           | 52                       | 32K +<br>32K                 | Oui               |

| G4                  | 1999  | 500                   |                             | 32 et 64                      |                              |                          |                              | Oui               |

| 2K (G5)             | 2001  | 1000                  |                             | 64                            |                              |                          |                              | Oui               |

# Microphotographie de la puce du 8086.

# LES MICROPROCESSEURS INTEL

#### 1 Les 8086 / 8088 / 80186 et 80188

#### 1.1 Architecture interne

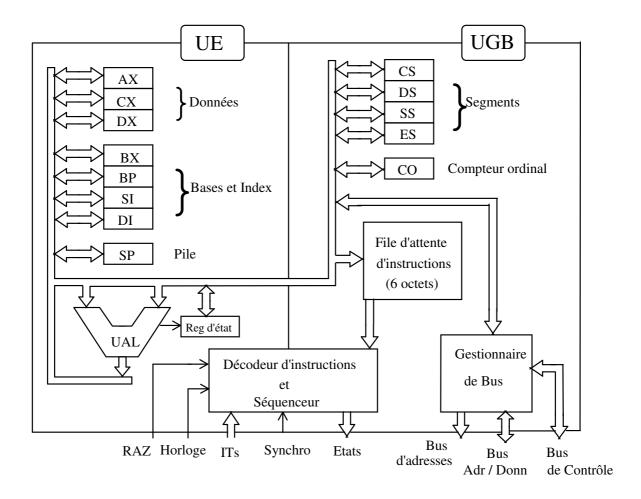

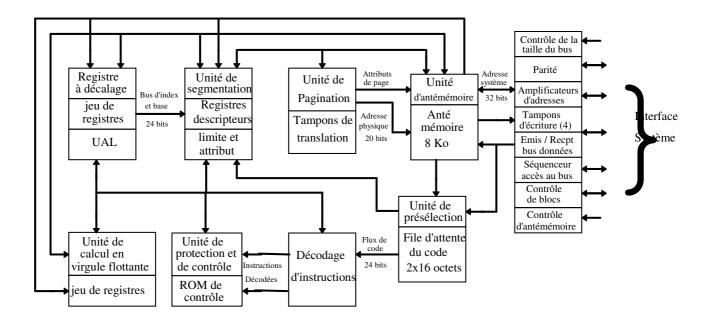

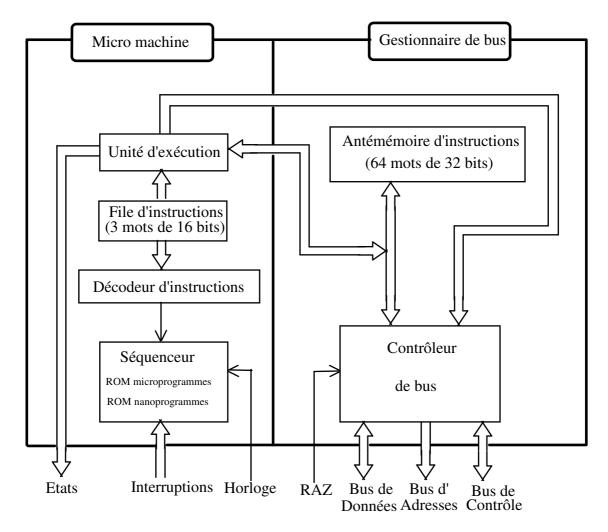

Le 8086 est constitué de 2 unités :

- L'unité de gestion des bus UGB

- L'unité d'exécution **UE**

Il peut être représenté par le schéma suivant :

#### Erreur! Les arguments du commutateur ne sont pas spécifiés. L'UGB se charge :

- de la recherche des instructions et de leur mise en file d'attente

- de la lecture et l'écriture des opérandes

- du calcul des adresses en mémoire

- du contrôle physique de la mémoire

Elle fonctionne en parallélisme total avec l'UE.

L'UE puise les instructions dans la file d'attente et utilise l'UGB pour obtenir ses opérandes depuis la mémoire et pour y ranger ses résultats. Tous les problèmes d'adressage sont donc gérés par l'UGB.

L'UGB divise la mémoire en 4 segments de 64K octets chacun désigné par l'un des registres de segment CS , DS , SS et ES.

CS désigne le segment contenant le code du programme c'est donc dans ce segment que sont recherchées les instructions

DS désigne le segment contenant les opérandes

SS désigne le segment associé à la pile dont le sommet est pointé par le registre SP. La pile est utilisée pour les adresses de retour et les paramètres de sous programme ainsi que pour sauvegarder et restituer les contextes lors d'interruptions.

ES désigne un segment supplémentaire de données.

Ces 4 segments peuvent se chevaucher et même être confondus. Les opérandes et les instructions sont référencées par un déplacement à l'intérieur de l'un de ces 4 segments. L'adresse réelle en mémoire est obtenue en ajoutant à ce déplacement le contenu du registre de segment multiplié par 16. Cet artifice permet d'accéder à lM octet  $(2^{20})$  de mémoire.

La mémoire est accessible octet par octet ou par mots de 16 bits. Toutefois l'accès à un mot de 16 bits se fait toujours en 2 transferts sur les 8088 et 80188 mais aussi sur les 8086 et 80186 lorsque l'adresse du mot est impaire. Il est donc utile, sur ces 2 derniers microprocesseurs, de veiller à "l'alignement" en adresses paires des opérandes 16 bits si l'on ne veut pas voir les performances chuter de façon importante.

Le 8088 ne diffère du 8086 que par les points suivants :

- La mémoire est organisée en octets et les accès aux opérandes 16 bits se font en 2 fois quelle que soit l'adresse.

- La file d'attente d'instructions est composée de 4 octets au lieu de 6.

- Le nombre d'accès à la mémoire étant presque multiplié par 2 les performances sont bien inférieures à celles du 8086

Le 80186 possède outre l'architecture interne du 8086 les éléments suivants :

- Un générateur d'horloge

- 2 canaux DMA (Direct Memory Acces) permettant de faire des transferts de mémoire à mémoire a mémoire à périphérique de façon totalement automatique.

- Un encodeur de priorité acceptant 4 lignes d'interruption (INT0 à INT3)

- 3 compteurs programmables autonomes (TIMERS) permettant la génération d'horloges ou de délais (watchdog par exemple).

- 6 lignes programmables de pré-décodage de boîtiers de mémoire permettant de simplifier la circuiterie externe.

- 7 lignes de pré-décodage de contrôleurs de périphériques programmables offrant les mêmes avantages que les précédentes.

- Un générateur programmable de cycles d'attente pour les mémoires et les contrôleurs de périphériques lents.

Les différences entre le 80188 et le 80186 sont les mêmes que celles décrites entre le 8088 et le 8086.

#### 1.2 Registres

Les 8086 et 8088 possèdent 14 registres de 16 bits :

AX accumulateur accessible en 2 fois 8 bits AH et AL il sert aux opérations arithmétiques et d'entrées/sorties

**DX** registre de données accessible en 2 fois 8 bits DH et DL, il est utilisé comme AX et pour les adresses d'entrées/sorties.

CX compteur accessible en 2 fois 8 bits CH et CL, il sert de comptage lors des instructions répétitives.

BX base accessible en 2 fois 8 bits BH et BL, il est registre de base dans le segment de données (DS).

**BP** registre de base dans le segment de pile (SS).

SI index de préférence associé au segment de données (DS).

DI index de préférence associé au segment de données supplémentaire (ES).

SP pointeur de pile associé au segment de pile (SS).

**CS** registre de segment de code.

DS registre de segment de données.

SS registre de segment de pile.

ES registre de segment de données supplémentaire.

CO compteur ordinal associé au segment de code (CS)

**SR** registre d'état contenant les indicateurs de l'UAL (signe, retenue, débordement, résultat nul, parité) ainsi que les bits associés aux interruptions et aux instructions répétitives.

Les 80186 et 80188 possèdent en outre :

- 2 fois 6 registres associés aux 2 canaux DMA

- 3 fois 4 registres associés aux 3 compteurs programmables (TIMERS)

- 5 registres associés aux pré-décodages et aux générateurs de cycles d'attente

- 16 registres associés au contrôleur d'interruptions

- Il faut ajouter à cette liste un registre permettant d'adresser les précédents.

## 1.3 Les opérandes

Les 8086, 8088, 80186 et 80188 traitent les opérandes suivants :

- Entiers naturels sur 8 et 16 bits

- Entiers relatifs sur 8 et 16 bits en complément à 2

- Caractères en ASCII sur 8 bits

- Chaînes de caractères de 1 à 64K codes ASCII

- Décimaux en représentation DCB sur 8 bits (1 ou 2 chiffres)

- Pointeurs constitués soit d'un déplacement sur 16 bits soit, sur 32 bits, d'un segment et d'un déplacement.

### 1.4 Les instructions

Les 8086 et 8088 possèdent les instructions suivantes :

### - Arithmétiques

Addition

Soustraction

ADD et ADC sur 8 et 16 bits

SUB et SBB sur 8 et 16 bits

- Multiplication MUL et IMUL sur 8 et 16 bits avec ou sans signe

- Division DIV et IDIV sur 16 et 32 bits sans signe et sur 16 bits avec signe

- Incrémentation INC sur 8 et 16 bits

Décrémentation

Changement de signe

DEC sur 8 et 16 bits

NEG sur 8 et 16 bits

- Extension de signe **CBW** et **CWD** sur 16 et 32 bits

#### - Logiques

| <ul> <li>Comparaison</li> </ul> | CMP  |

|---------------------------------|------|

| - Test de bit                   | TEST |

| - Non                           | NOT  |

| - Ou                            | OR   |

| - Et                            | AND  |

| - Ou exclusif                   | XOR  |

Toutes ces opérations portent sur des opérandes 8 ou 16 bits. On se référera au chapitre 3.3.4 pour plus de détail sur les opérations TEST et CMP.

#### - Transferts

Chargement d'un registre

Rangement d'un registre

MOV 8 ou 16 bits selon le registre

MOV 8 ou 16 bits selon le registre

- Empilement de 16 bits- Dépilement de 16 bitsPOP

- Echange entre registres et mémoire XCHG 8 ou 16 bits selon le registre

- Lecture d'un caractère dans une chaîne XLAT (le début de la chaîne est pointé par BX et le rang du caractère est dans AL)

- Chargement d'une adresse dans un registre **LEA** (au lieu de recevoir la valeur comme avec MOV le registre reçoit l'adresse)

- Chargement d'une adresse de segment dans DS et d'un déplacement dans un registre LDS

- Chargement d'une adresse de segment dans ES et d'un déplacement dans un registre LES

## - Décalages

Logique à droite et à gauche

Arithmétique à droite et à gauche

SAR

SAL

- Circulaire à droite et à gauche ROR ROL RLC RCR

Le nombre de décalages est spécifié dans CL, l'opérande est sur 8 ou 16 bits.

#### - Ruptures de séquence

- Branchement inconditionnel **JMP**

- Branchements conditionnels :

si égal **JE** si différent **JNE**

si < JB entre entiers naturel JL entre entiers relatifs si < ou = JBE entre entiers naturels JLE entre entiers relatifs si > JA entre entiers naturels JG entre entiers relatifs si > ou = JAE entre entiers naturels JGE entre entiers relatifs

si débordement

si non débordement

si négatif

si positif

si parité fausse

si parité juste

si CX est nul

JO

JNO

JNO

JNS

si parité fausse

JNP

si CX est nul

JCXZ

- Appel de sous programme **CALL** - Retour de sous programme RET - Appel d'interruption INT - Retour d'interruption **IRET**

- Appel de l'interruption relative au débordement INT0

- Attente d'interruption WAIT

- Répéter en décrémentant CX tant que CX est différent de zéro LOOP

- Répéter en décrémentant CX tant que CX est différent de zéro et que l'indicateur d'égalité n'est pas positionné: **LOOPNE**

- Répéter en décrémentant CX tant que CX est différent de zéro et que l'indicateur d'égalité est positionné: LOOPE

## - Opérations sur le registre d'état

- Transferts avec AH LAHF SAHF - Empilement **PUSHF** - Dépilement **POPF** - Mise à 0/1 de la retenue CLC **STC**

- Complémentation de la retenue **CMC**

- Mise à 0/1 du bit de direction 11 CLD **STD**

- Masquage/démasquage des interruptions CLI STI

#### - Instructions d'Entrée/Sortie

- Lecture sur 8 ou 16 bits dans AL ou AX: IN - Ecriture des 8 ou 16 bits de AL ou AX : OUT

#### - Manipulation de caractères

- Transfert d'un ou 2 caractères pointés par SI dans celui ou ceux pointés par DI et mise à jour de SI et DI: **MOVS**

- Idem avec répétition tant que CX est différent de 0. CX étant automatiquement décrémenté : **REP MOVS**

- Chargement d'un ou 2 caractères pointés par SI dans AL ou AX et mise à jour automatique de SI : **LODS**

- Rangement d'un ou 2 caractères contenus dans AL ou AX dans la zone pointée par DI et mise à jour de DI: **STOS**

- Comparaison d'un ou 2 caractères pointés par DI avec le contenu de AL ou AX et mise à jour de DI :

- Idem avec répétition tant que CX est différent de 0 et non égalité. CX étant automatiquement REPNE SCAS décrémenté:

- Idem avec répétition tant que CX est différent de 0 et égalité. CX étant automatiquement **REPE SCAS** décrémenté:

- Comparaison d'un ou 2 caractères pointés par DI avec un ou 2 caractères pointés par SI avec mise à jour de DI et SI : CMPS

<sup>11</sup> La valeur de ce bit détermine le sens dans lequel sont traitées les chaînes de caractères (droite à gauche ou gauche à droite) par les instructions décrites plus loin.

- Idem avec répétition tant que CX est différent de 0 et non égalité. CX étant automatiquement décrémenté : **REPE CMPS**

- Idem avec répétition tant que  $\operatorname{CX}$  est différent de 0 et égalité.  $\operatorname{CX}$  étant automatiquement décrémenté

: REPE CMPS

La mise à jour des pointeurs SI et DI est faite par addition ou soustraction selon la valeur du bit de direction du registre d'état de 1 ou 2 selon que l'instruction traite 1 ou 2 caractères (8 ou 16 bits)

## - Instructions de contrôle

- Synchronisation avec un coprocesseur **ESC**

- Verrouillage du bus dans un système multi-microprocesseurs **LOCK**

Arrêt du microprocesseurAttente d'interruptionWAIT

#### - Instructions supplémentaires

Les 80186 et 80188 possèdent quelques possibilités supplémentaires :

- Empilement de tous les registres PUSHA

- Dépilement de tous les registres POPA

- Lecture de caractères depuis un périphérique INS 12

- Ecriture de caractères vers un périphérique OUTS <sup>1</sup>

- Préparation de la pile pour passage de paramètres **ENTER**

- Restitution de la pile après passage de paramètres LEAVE

- Vérification de non dépassement de limite (taille de tableau ou de chaîne de caractères par exemple) **BOUND**

#### 1.5 La mémoire et l'adressage

Le bus d'adresses est de 20 bits donc l'espace mémoire ne peut excéder lM octets (2<sup>20</sup>).Les bus d'adresses et de données partagent les mêmes lignes physiques et sont donc multiplexés dans le temps.

Le fonctionnement lors d'un accès à la mémoire est le suivant :

- Durant la 1<sup>ère</sup> période d'horloge l'adresse est émise accompagnée d'un signal (ALE) permettant d'en mémoriser la valeur dans un registre externe (les lignes d'adresses deviendront des lignes de données par la suite en raison du multiplexage).

- Durant la 2<sup>ème</sup> période d'horloge le signal indiquant s'il s'agit d'une lecture ou d'une écriture est émis. Lors d'une écriture c'est aussi pendant cette période que le bus de données reçoit la valeur à écrire.

- La 3<sup>ème</sup> période d'horloge voit s'effectuer le transfert avec la mémoire. Si celle-ci est trop lente un signal spécial (READY) doit être envoyé au microprocesseur de façon à ce qu'il insère des périodes d'horloge d'attente entre cette 3<sup>ème</sup> période et la suivante.

- Durant la 4<sup>ème</sup> période tous les signaux et le bus retrouvent leur état de repos.

La possibilité d'insérer des cycles d'attente entre la 3<sup>ème</sup> et la 4<sup>ème</sup> période d'un accès à la mémoire est la caractéristique des microprocesseurs à bus asynchrone (ce qui n'était pas le cas de la plupart des 8 bits).

On a déjà vu en 1.1 que la mémoire est ensuite divisée en segments de 64K octets et que l'accès est souvent fait en 2 fois 8 bits même sur un 8086 ou un 80186 en raison des problèmes d'alignement en adresses paires.

Les 8086, 8088, 80186 et 80188 possèdent les modes d'adressage suivants :

12 Les instructions INS et OUTS fonctionnent comme STOS et LODS à la différence que le rôle de AL ou AX est tenu par le périphérique dont l'adresse est dans DX. Elles peuvent être répétées tant que CX est différent de 0 avec décrémentation de CX par : REP INS ou REP OUTS

Les Microprocesseurs

M. DALMAU, IUT de Bayonne

- inhérent ou registre : Soit l'instruction n'a pas d'opérande soit l'opérande est dans un registre

- immédiat : La valeur de l'opérande est dans l'instruction sur 8 ou 16 bits

- **direct ou étendu** : L'opérande est désigné par son adresse relative au début du segment soit sur 8 bits (direct) soit sur 16 bits (étendu).

- avec base : L'opérande est désigné par son adresse relative au début du segment obtenue soit par le contenu d'un registre de base BP ou BX soit par la somme d'un registre de base BP ou BX et d'un déplacement sur 8 ou 16 bits contenu dans l'instruction

- avec index : L'opérande est désigné par son adresse relative au début du segment obtenue soit par le contenu d'un registre d'index SI ou DI soit par la somme d'un registre d'index SI ou DI et d'un déplacement sur 8 ou 16 bits contenu dans l'instruction

- $\hbox{-} \textbf{avec base et index}: L'opérande est désigné par son adresse relative au début du segment obtenue soit par la somme d'un registre de base BP ou BX et d'un registre d'index SI ou DI. soit par la somme d'un registre de base BP ou BX , d'un registre d'index et d'un déplacement sur 8 ou 16 bits contenu dans l'instruction$

- **relatif** : Ce mode n'est utilisable qu'avec les instructions de rupture de séquence. L'instruction contient un déplacement fixe constitué d'un entier relatif sur 8 ou 16 bits qui sera ajouté au contenu du compteur ordinal pour calculer l'adresse de la prochaine instruction.

- **indirect mémoire** : Ce mode n'est utilisable qu'avec les instructions de branchement inconditionnel. L'instruction désigne un opérande 16 bits qui est placé dans le CO (saut intrasegment) ou un opérande 32 bits dont le premier mot est placé dans CS et le deuxième dans CO (saut extra-segment).

<u>Remarque</u> La littérature consacrée au 8086 (même celle du constructeur) ne décrit généralement pas ces 2 derniers modes dans la mesure où ils ne sont liés qu'aux instructions de rupture de séquence et par conséquent ne sont pas disponibles pour l'accès aux opérandes.

#### 1.6 L'horloge

L'horloge de séquencement des 8086 et 8088 peut être de 4, 5, 8, 10 ou 12 MHz alors que le 80186 peut utiliser une horloge de 6, 8, 10, 12.5, 16 ou 20 MHz.

Il devient très difficile, sur ce type de microprocesseurs, de mesurer la durée d'une instruction en effet plusieurs paramètres entrent en jeu :

- L'instruction est ou pas déjà dans la file d'attente (il faut tenir compte du fait que l'UGB fait de la prédiction d'instructions "en aveugle" et ne prévoit pas les ruptures de séquence. A chaque fois qu'un saut est effectué il faut remplir à nouveau la file d'instructions).

- Des cycles d'attente ont lieu ou pas lors des accès à la mémoire.

- L'accès à la mémoire est fait en 1 ou 2 transferts (problème des adresses impaires).

#### 1.7 Les Entrées/Sorties

Les instructions d'entrée/sortie activent des lignes de contrôle spécifiques aux périphériques et permettent d'adresser jusqu'à 64K octets (un contrôleur de périphérique occupe entre 2 et 32 octets en moyenne).

## 1.8 Les interruptions

Il existe une table (placée en mémoire à partir de l'adresse physique 0) contenant 256 vecteurs (un vecteur est formé de 2 mots de 16 bits : segment et déplacement) associée aux interruptions.

Une interruption peut être provoquée de façon logicielle ou matérielle :

- logicielle, c'est l'instruction INT suivie du n° de l'interruption à traiter

- matérielle, c'est l'activation de la ligne IRQ suivie de l'émission sur le bus de données du n° de l'IT (cette valeur est placée sur le bus par l'auteur de l'interruption en réponse à une sollicitation du microprocesseur).

La prise en compte d'une IT se traduit par la sauvegarde du point de retour et du registre d'état dans la pile suivie du branchement au sous-programme désigné dans la table de vecteurs.

Certains vecteurs de cette table sont associés à des événements particuliers :

- Division par zéro

- -1: Mode pas à pas, lorsqu'il est mis dans ce mode le microprocesseur exécute une interruption de type 1 après chaque instruction (trace)

- -2: Associé à la ligne NMI (Non Maskable Interrupt)

- -3: Utilisé lors des mises au point pour insérer des points d'arrêt

- -4: Associé à l'instruction INTO, elle est exécutée si l'indicateur de débordement est positionné

Les suivants n'existent que sur les 80186 et 80188

- 5: Associé à l'instruction BOUND de vérification de limites

- -6: Généré lors de la découverte d'un code opération inconnu

- -7: Associé à l'instruction ESC lorsqu'il n'y a pas de coprocesseur

- -8: Associé au ler compteur (TIMER)

- Associé au ler canal DMA - 10:

- Associé au 2<sup>ème</sup> canal DMA - 11:

- 12 : Ligne INT0 externe

- 13: Ligne INTl externe

- Ligne INT2 externe - 14:

- 15 : Ligne INT3 externe

- Associé au 2<sup>ème</sup> compteur (TIMER) Associé au 3<sup>ème</sup> compteur (TIMER) - 18:

- 19 :

#### 1.9 Sémaphores

L'instruction LOCK permet de verrouiller les bus dans un système multiprocesseurs (autre microprocesseur, unité d'échange ou canaux DMA). Grâce à cette instruction on peut réaliser des séquences lecture/modification/ écriture en mémoire sans risquer de conflits (sémaphores).

### 1.10 Compatibilité

| Marque  | Référence | Horloge (MHz) |

|---------|-----------|---------------|

| AMD     | Am8086    | 5 8 10        |

| Harris  | HS80C86   | 5 8 10        |

| Siemens | SAB8086   | 8 10          |

| AMD     | Am8088    | 5 8 10        |

| Harris  | HS80C88   | 5 8 10        |

| AMD     | Am80L188  | 16            |

| NEC     | V30       | 10 12 16      |

| Siemens | SAB80186  | 8 10 16       |

| AMD     | Am80L188  | 16            |

| NEC     | V20       | 8 10          |

| Siemens | SAB80188  | 8 10          |

|                      | Microphotographie de la puce du 80286. |                            |  |

|----------------------|----------------------------------------|----------------------------|--|

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

|                      |                                        |                            |  |

| Les Microprocesseurs |                                        | M DAI MAII IIIT de Rayonne |  |

#### 2.1 Architecture interne

On retrouve dans le 80286 les 2 unités du 8086 :

- Unité de gestion de bus- Unité d'exécutionUE

auxquelles ont été ajoutées 2 nouvelles unités :

- Unité d'instructions- Unité d'adressesUA

L'unité d'instructions UI puise dans la file d'attente de 6 octets de l'UGB pour maintenir à jour une file d'attente de 3 instructions décodées.

L'unité d'adresses UA assure le calcul des adresses physiques tant en mode réel qu'en mode virtuel.

Le 80286 peut fonctionner en adressage réel il est alors totalement compatible au niveau du code avec les 8086, 8088, 80186 et 80188.

Il peut aussi fonctionner en adressage virtuel avec protections.

#### 1°) Mode réel

Dans ce mode, le fonctionnement est identique à celui décrit pour le 8086. On retrouve les 4 segments de 64K octets. Bien que le 80286 puisse adresser 16M octets (2<sup>24</sup>) de mémoire seuls lM octets sont accessibles en mode réel (pour la compatibilité avec le 8086).

On peut considérer qu'en mode réel le 80286 n'est qu'un 8086 amélioré et environ 2,5 fois plus rapide.

#### 2°) Mode virtuel protégé

Le 80286 passe en mode virtuel protégé par la mise à 1 d'un bit du registre mot d'état.

Chaque tâche dispose alors d'un giga octets (2<sup>30</sup>) de mémoire virtuelle placée dans 16M octets (2<sup>24</sup>) de mémoire réelle.

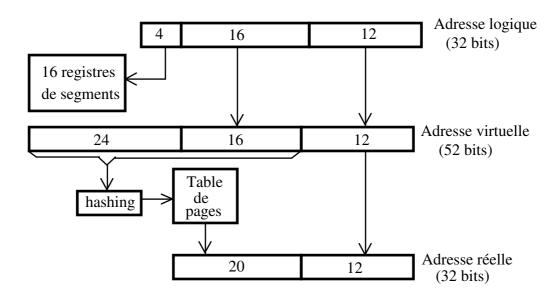

L'adresse est constituée d'un sélecteur et d'un déplacement.

Le sélecteur (16 bits) désigne une table de descripteurs et une entrée dans celle-ci.

Le descripteur (48 bits) contient, outre l'adresse de base en mémoire et la taille de la page de mémoire virtuelle, des indications concernant les droits d'accès à cette page.

Le déplacement est ajouté à cette adresse de base pour constituer l'adresse physique.

Le 80286 utilise comme sélecteurs les 4 registres de segments CS DS SS et ES. Il possède en outre 4 registres de 48 bits contenant le descripteur associé à chacun de ces sélecteurs. La mise à jour de ces registres est automatiquement faite par le 80286 à chaque modification des sélecteurs par accès aux tables en mémoire.

Il existe 3 tables de descripteurs décrites chacune par un registre de 40 bits dont un champ de 24 bits pointe sur le début de la table en mémoire et un second champ de 16 bits donne la taille de la table. Les 3 tables sont les suivantes :

- Table globale GDT contenant les descripteurs des pages accessibles par toutes les tâches.

- Table locale LDT contenant les descripteurs des pages propres à une tâche.

- Table d'interruptions IDT contenant les descripteurs des procédures d'interruption (256 interruptions)

#### 2.2 Les registres

Le 80286 possède les 14 registres de 16 bits du 8086 dont le rôle est le même, exception faite de l'utilisation en tant que sélecteurs des registres de segments en mode virtuel.

Le 80286 contient de plus les registres suivants :

**MSW**: Mot d'état (16 bits) 4 bits seulement sont utilisés pour le passage en mode virtuel, le changement de tâche et pour indiquer la présence ou l'absence d'un coprocesseur (instruction ESC).

**GDTR**: Descripteur de la table globale (24 bits d'adresse et 16 bits de longueur)

**LDTR**: Descripteur de la table locale (24 bits d'adresse et 16 bits de longueur)

**IDTR**: Descripteur de la table d'interruption (24 bits d'adresse et 16 bits de longueur)

CSDC: copie du descripteur dont le sélecteur est CS (48 bits)

**DSDC**: copie du descripteur dont le sélecteur est DS (48 bits)

**SSDC**: copie du descripteur dont le sélecteur est SS (48 bits)

ESDC: copie du descripteur dont le sélecteur est ES (48 bits)

TR: sélecteur associé à la tâche courante (16 bits) désigne dans la table locale ou globale un descripteur de tâche

**TRB** : Adresse de base de la table d'état de la tâche courante (24 bits)

TRL: Taille de la table d'état de la tâche courante (16 bits)

Remarque: Le registre d'état SR utilise 3 bits supplémentaires :

- 2 pour décrire le niveau de privilège nécessaire à l'utilisation des instructions d'entrée/sortie (voir 2.7).

- 1 (bit NT) pour l'enchaînement des tâches (voir 2.8).

#### 2.3 Les opérandes

Le 80286 traite les mêmes opérandes que le 8086 (cf 1.3)

#### 2.4 Les instructions

On retrouve tout le jeu d'instruction du 80186 (cf 1.4) auquel sont venues s'ajouter les instructions relatives aux tâches et à la mémoire virtuelle.

CTS: Remise à 0 du bit TS du mot d'état. Ce bit est mis à 1 par le 80286 lors d'un changement de tâche de façon à noter qu'il sera probablement nécessaire de changer le contexte des coprocesseurs s'ils doivent être utilisés par la nouvelle tâche. Si ce bit est à 1 et qu'un coprocesseur doit être utilisé le 80286 exécutera une interruption de type 7.

CTS sera donc utilisée par le programmeur après avoir mis à jour le contexte des coprocesseurs.

**LGDT**: Chargement du descripteur de table globale dans GDTR

LIDT: Chargement du descripteur de table globale dans IDTR

LLDT: Chargement du descripteur de table globale dans LDTR

SGDT: Rangement du descripteur de table globale GDTR

**SIDT**: Rangement du descripteur de table globale IDTR

$\boldsymbol{SLDT}$  : Rangement du descripteur de table globale LDTR

LTR : Chargement du registre TR STR : Rangement du registre TR

Toute modification de TR provoque un accès à la table locale ou globale permettant de lire le descripteur de tâche et de mettre à jour les registres TRB et TRL

LMSW: Chargement du mot d'état MSW SMSW: Rangement du mot d'état MSW

LAR: Place dans l'opérande l'octet du descripteur associé au sélecteur spécifié décrivant les droits d'accès

LSL : Place dans l'opérande le double octet du descripteur associé au sélecteur spécifié contenant la taille du segment

**ARPL** : Ajuste le niveau de privilège du sélecteur désigné à celui décrit dans l'opérande (cette instruction ne peut que diminuer le niveau initial)

**VERR** : Vérifie si le segment décrit par le sélecteur spécifié peut être lu

**VERW** : Vérifie si le segment décrit par le sélecteur spécifié peut être écrit

$\underline{Remarque}$ : Pour les 5 dernières instructions se reporter à la description des descripteurs en 2.5 et des privilèges en 2.6

#### 2.5 L'adressage de la mémoire

Les principes d'accès à la mémoire ont été décrits en 2.1.

En mode réel le 80286 possède exactement les mêmes types d'adressage que le 8086 (cf 1.5).

En mode virtuel les modes d'adressage sont encore les mêmes à la seule différence que les registres de segments sont utilisés comme sélecteurs pour accéder à des descripteurs de segments.

Nous allons maintenant décrire plus en détail le contenu des sélecteurs et des descripteurs.

#### 1°) Sélecteurs

Ils sont constitués de 3 champs :

- Champ RPL, sur 2 bits, décrit le niveau de privilège (0 à 3)

- Champ TI sur 1 bit désigne la table de descripteurs globale ou locale

- Champ index sur 13 bits contient l'entrée dans la table

#### 2°) Descripteurs

Un descripteur est constitué de 64 bits dont 48 seulement sont utilisés. On distingue 3 types de descripteurs :

### - Descripteur de segment de code et données

Il est utilisé pour les segments de code, de données et de pile. Il est constitué de 3 champs :

- Adresse de base du segment en mémoire (24 bits)

- Taille du segment (16 bits)

- Droits d'accès au segment (8 bits) formé de :

- P : un bit de présence du segment en mémoire

- DPL : 2 bits, privilège associé au segment (0 à 3)

- S : un bit, mis à 1 pour distinguer les descripteurs de segment de codes et données des descripteurs de segments du système (voir ci-dessous)

- Type : 3 bits, protections en lecture/écriture et exécution

- A : un bit, utilisation du segment, permet la mise en place de stratégies de remplacement de segments

#### - Descripteur de segment du système

Il est utilisé pour décrire les segments contenant les tables de descripteurs locales et les tables d'état de tâches. Il est constitué de 3 champs :

- Adresse de base du segment en mémoire (24 bits)

- Taille du segment (16 bits)

- Droits d'accès au segment (8 bits) formé de :

- P : un bit de validité du contenu du descripteur

- DPL : 2 bits, privilège associé au segment (0 à 3)

- S: un bit, mis à 0 (voir ci-dessus)

- Type : 4 bits : 1 Table d'état de tâche disponible

2 Descripteur de table locale3 Table d'état de tâche occupée

#### - Descripteur de point d'entrée

Il est utilisé pour contrôler des points d'entrée liés à des sous-programmes, des tâches, des interruptions ou des erreurs (traps ou exceptions). Il est constitué de 4 champs :

- Sélecteur du segment de destination (16 bits)

- Déplacement dans le segment de destination (14 bits)

- Compte de mots (sur 5 bits) : nombre de mots à transférer de la pile d'origine à celle de destination lors de l'appel de sous-programme

- Droits d'accès au segment (8 bits) formé de :

- P : un bit de validité du contenu du descripteur

- DPL : 2 bits, privilège associé au segment (0 à 3)

- S: un bit, mis à 0 (voir ci-dessus)

- Type : 4 bits : 4 Point d'entrée de sous-programme

- 5 Point d'entrée de tâche

- 6 Point d'entrée d'interruption

- 7 Point d'entrée d'exception

## 2.6 Les privilèges

Le 80286 gère 4 niveaux de privilège qui contrôlent l'utilisation d'instructions particulières et l'accès aux descripteurs et à leurs segments associés

Ces 4 niveaux sont prévus pour l'utilisation suivante :

niveau 0 : noyau du système d'exploitation niveau 1 : primitives du système d'exploitation

niveau 2 : extensions du système d'exploitation

niveau 3: applications

Les niveaux de privilèges apparaissent en 3 lieux :

#### 1°) Privilèges de tâche

Il est défini par le champ RPL du registre CS. Il ne peut être modifié que par le passage à travers un point d'entrée (appel de sous programme, changement de tâche, interruption, exception).

Quand une tâche est activée, son contexte est pris dans la table d'état de tâche (TSS). Cette table est décrite par un descripteur de segment du système (type 3) placé dans la table globale ou locale et pointé par le registre TR. En réalité, ce descripteur est recopié par le 80286 dans les registres TRB et TRL chaque fois que le contenu de TR est modifié.

Le contexte associé à une tâche contient les valeurs de chacun des registres du 80286 (y compris CS dont le champ RPL détermine le privilège de la tâche) et le descripteur de la table locale (LDT) appartenant à la tâche.

#### 2°) Privilège de descripteur

Il est contenu dans les 2 bits DPL du champ "droits d'accès du descripteur".

Il définit le niveau de privilège nécessaire pour accéder à ce descripteur (le niveau de privilège de la tâche courante doit être supérieur ou égal à DPL).

Les descripteurs de la table locale (LDT) échappent à cette règle puisqu'ils ne sont accessibles que par la tâche propriétaire de cette table locale.

#### 3°) Privilège de sélecteur

Il est défini par le champ RPL d'un sélecteur. Il détermine le niveau de privilège nécessaire pour utiliser ce sélecteur.

Remarque : Le privilège du sélecteur CS est le privilège de la tâche.

#### 2.7 La protection

Le 80286 assure la sécurité en interdisant l'utilisation des instructions LIDT , LLDT , LGDT , LTR , LMSW , CTS et HLT aux tâches dont le niveau de privilège est non nul.

De même, les instructions INS , IN , OUTS , OUT , STI , CLI et LOCK sont interdites aux tâches dont le niveau de privilège est inférieur à la valeur contenue dans le registre d'état.

#### 2.8 Le changement de tâche

Il peut être obtenu par les instructions JMP ou CALL faisant référence à la table d'état des tâches ou à un descripteur de point d'entrée de tâche (type 5) dans la table locale (LDT) ou globale (GDT).

Il peut aussi être obtenu par une interruption logicielle (INT) ou matérielle (ligne physique) ou d'exception (erreur) qui fera référence à un descripteur de point d'entrée de tâche dans la table d'interruptions (IDT).

Le changement de tâche consiste en une sauvegarde du contexte courant dans la table d'état de la tâche courante (TSS) et en un chargement du nouveau contexte depuis la TSS de la nouvelle tâche.

L'instruction IRET provoque le retour à la tâche qui a appelé la tâche courante ou qui a été interrompue. La valeur du bit NT du registre d'état permet au 80286 de distinguer ces 2 cas.

#### 2.9 Les interruptions

Comme le 8086, le 80286 connaît 256 interruptions pouvant être appelées de façon logicielle ou matérielle. Parmi ces interruptions certaines sont associées à des événements particuliers :

- 0 à 7 : même utilisation que dans le 8086 (voir 1.8)

- 8 : en mode réel : n° d'IT dépassant les limites de la table

en mode virtuel : 2 exceptions ont été détectées au cours de la même instruction

- 9 : Débordement du segment par le coprocesseur

- 10 : En mode virtuel seulement : table d'état de tâche incorrecte

- 11 : En mode virtuel seulement : segment de mémoire virtuelle non présent en mémoire physique

- 12 : En mode virtuel seulement : débordement de la pile ou segment de pile non présent en mémoire physique.

- 13 : En mode réel : débordement de segment En mode virtuel : violation de protection ou tentative de passage à un niveau de privilège supérieur

#### 2.10 L'horloge

Le temps d'exécution d'une instruction est, en général, le même en mode réel et en mode virtuel en raison de l'existence de l'unité d'adresse qui effectue tous les calculs avec une architecture de pipe-line et des registres contenant des copies des descripteurs.

La fréquence d'horloge peut être 6, 8, 10, 12, 16 ou 20MHz.

# 2.11 Compatibilité

| Marque  | Référence | Horloge (MHz)    |

|---------|-----------|------------------|

| AMD     | Am80286   | 8 10 12 16 20    |

| Harris  | HS80C286  | 10 12.5 16 20 25 |

| Siemens | SAB80286  | 8 10 12 16       |

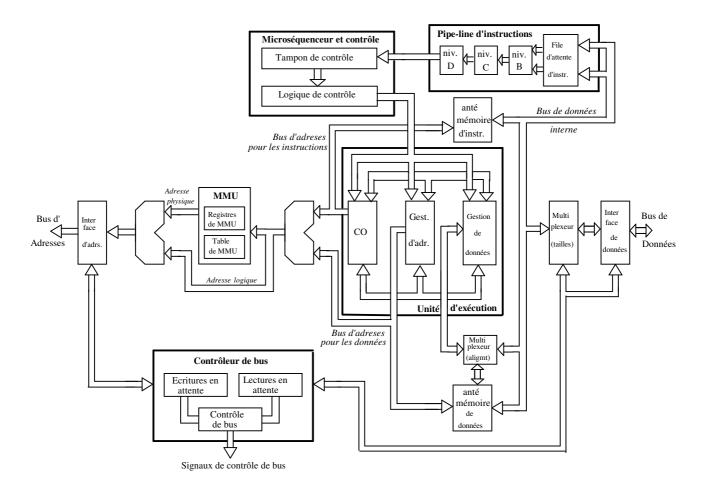

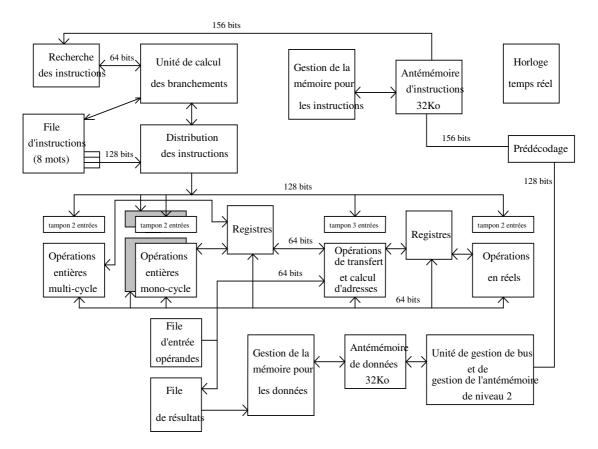

#### 3.1 Architecture interne

Le 80386 est composé de 4 unités :

- **Unité de gestion de bus** (UGB) qui assure la prédiction d'instructions dans une file d'attente de 16 octets ainsi que le contrôle physique des bus

- Unité d'exécution (UE) qui contient les 8 registres de 32 bits d'usage général et l'UAL

- **Unité d'instructions** (UI) qui puise dans la file d'attente de l'UGB pour maintenir à jour une file d'attente de 2 instructions décodées

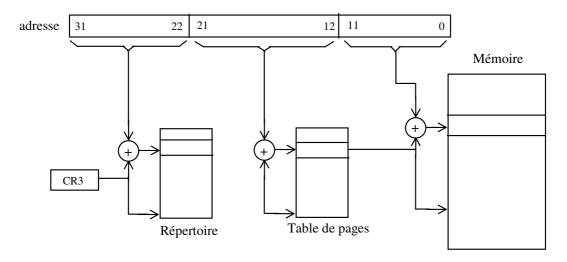

- Unité de gestion de mémoire (MMU) elle même constituée de 2 unités :

- l'unité de segmentation qui gère les adresses logiques et les protections

- l'unité de pagination qui gère les adresses physiques et effectue les calculs associés

Comme le 80286, le 80386 peut fonctionner en 2 modes :

#### 1°) Mode réel

Dans ce mode, il apparaît comme un 8086 doté d'extensions 32 bits Bien que le 80386 puisse adresser 4G octets (2<sup>32</sup>) de mémoire, seuls lM octets sont accessibles en mode réel.

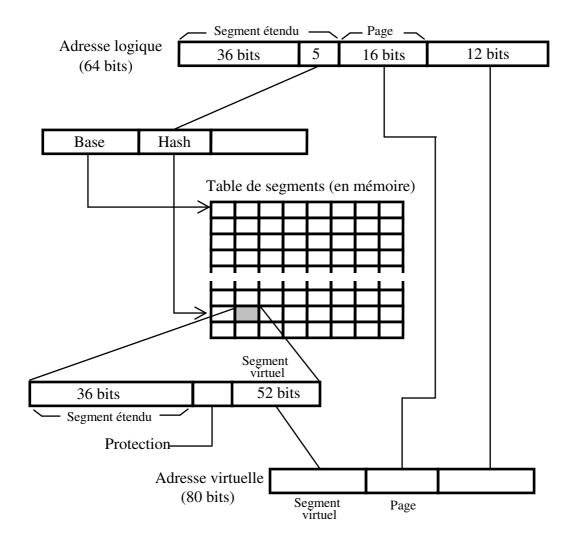

#### 2°) Mode virtuel protégé

Dans ce mode, le 80386 dispose de 64T octets (2<sup>46</sup>) de mémoire virtuelle placés dans les 4G octets (2<sup>32</sup>) de mémoire physique.

Le fonctionnement du mode virtuel du 80386 est semblable à celui de 80286 les seules différences étant les suivantes :

- Les descripteurs contiennent une adresse sur 32 bits au lieu de 24 et une taille sur 20 bits au lieu de 16

- Le nombre de types placés dans les droits d'accès des descripteurs de segments du système a été augmenté pour différencier les tables d'état de tâche au format 80286 de celles au format 80386 (ces dernières étant plus grandes puisque le 80386 a plus de registres et qu'ils sont de taille supérieure). INTEL a choisi de conserver la possibilité de gérer des tables de type 80286 afin de garder la plus totale compatibilité entre le 386 et le 286.

- Le nombre de types placés dans les droits d'accès des descripteurs de points d'entrée a été augmenté pour les mêmes raisons que précédemment.

- L'adresse calculée à partir du sélecteur et du déplacement peut ne pas constituer directement l'adresse réelle (comme c'était le cas dans le 80286) lorsque l'unité de pagination est mise en oeuvre (voir 3.6)

## 3.2 Les registres

Les registres du 80386 sont les suivants :

## \* 8 registres d'usage général

**EAX** : sur 32 bits, les 16 bits de faible poids étant désignés par AX (divisé en AH et AL) il a le même rôle que AX

EDX: sur 32 bits, même remarque que ci-dessus pour DX

ECX: sur 32 bits, même remarque que ci-dessus pour CX

**EBX**: sur 32 bits, même remarque que ci-dessus pour BX

**ESI**: sur 32 bits, les 16 bits de faible poids étant désignés par SI, il a le même rôle que SI

EDI: sur 32 bits, même remarque que ci-dessus pour DI

EBP: sur 32 bits, même remarque que ci-dessus pour BP

ESP: sur 32 bits, même remarque que ci-dessus pour SP

#### \* 6 registres de segments

CS: sur 16 bits, segment ou sélecteur de code

SS: sur 16 bits, segment ou sélecteur de pile

DS: sur 16 bits, segment ou sélecteur de données

ES: sur 16 bits, segment ou sélecteur de données supplémentaire

FS: sur 16 bits, segment ou sélecteur de données supplémentaire

**GS**: sur 16 bits, segment ou sélecteur de données supplémentaire

#### \* Le compteur ordinal et le registre d'état

**ECO**: sur 32 bits, compteur ordinal

**ESR** : sur 32 bits, registre d'état qui contient les mêmes indicateurs que celui du 80286 auxquels ont été ajoutés 2 bits:

- VM indiquant l'utilisation du mode virtuel en émulation du 8086

- RF utilisé en phase de mise au point

\* A ces extensions 32 bits du 80286, il faut ajouter les 4 registres de description de tables **GDTR**, **LDTR**, **IDTR** et **TR** et les copies associées **CSDC**, **DSDC**, **SSDC**, **ESDC**, **TRB** et **TRL** auxquels viennent encore s'ajouter les copies associées aux 2 registres de segments supplémentaires **FSDC** et **GSDC**.

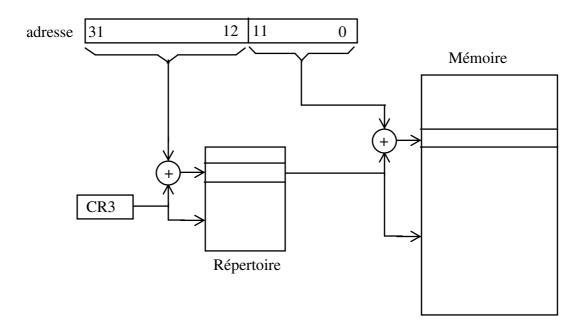

### \* Le 80386 contient en outre 4 registres de contrôle