# COMPOSANTS NON LINÉAIRES À SEMI-CONDUCTEURS

# PREMIÈRE ANNÉE DE L'ESPCI

JÉRÔME LUCAS

6 décembre 2017

Ce polycopié du cours d'électronique de l'ESPCI réalisé avec LAT $_E$ X  $2_{\mathcal{E}}$  est mis à votre disposition sous la licence ouverte conçue par Etalab.

OPEN LICENCE

www.etalab.gouv.fr/wp-content/uploads/2014/05/Licence\_Ouverte.pdf www.etalab.gouv.fr/wp-content/uploads/2014/05/Open\_Licence.pdf

# Table des matières

| 1 | Sem   | ni-conducteurs                                                                 | 6  |

|---|-------|--------------------------------------------------------------------------------|----|

|   | 1.1   | Bases élémentaires de la théorie des bandes                                    | 6  |

|   | 1.2   | Principaux semi-conducteurs utilisés en électronique                           | 6  |

|   |       | 1.2.1 Exemple du silicium                                                      | 6  |

|   |       | 1.2.2 Conduction par trous                                                     | 7  |

|   |       | 1.2.3 Recombinaisons électrons-trous                                           | 8  |

|   | 1.3   | Dopages                                                                        | 8  |

|   |       | - * - * - * - * - * - * - * - * - * - *                                        |    |

| 2 | La j  | ionction PN                                                                    | 8  |

|   | 2.1   | Écrantage                                                                      | 10 |

|   | 2.2   | La jonction PN comme composant électronique : La diode                         | 10 |

|   | 2.3   | Caractéristique statique courant/tension de la diode                           | 11 |

|   |       |                                                                                |    |

| 3 | Utili | isation des diodes                                                             | 12 |

|   | 3.1   | Stratégies de calcul                                                           | 14 |

|   | 3.2   | Droite de charge                                                               | 15 |

|   | 3.3   | Montages de base                                                               | 15 |

|   |       | 3.3.1 Redressement simple alternance                                           | 15 |

|   |       | 3.3.2 Redressement double alternance                                           | 16 |

|   |       | 3.3.3 Écrêtage (clamping)                                                      | 16 |

|   |       | 3.3.4 Détection de crêtes                                                      | 17 |

|   |       | 3.3.5 Logique à diodes                                                         | 17 |

|   |       | 3.3.6 Diode de roue libre                                                      | 17 |

|   |       | 3.3.7 Pompe à diode                                                            | 18 |

|   |       |                                                                                |    |

| 4 | Autı  | res types de diodes                                                            | 22 |

|   | 4.1   | Diodes Zener                                                                   | 22 |

|   | 4.2   | Diodes Électroluminescentes (LED)                                              | 23 |

|   | 4.3   | Varicaps                                                                       | 24 |

|   | 4.4   | Diodes PIN                                                                     | 24 |

|   | 4.5   | Diodes Schottky                                                                | 25 |

|   | 4.6   | Diodes GUN (Hyperfréquences)                                                   | 25 |

|   |       |                                                                                |    |

| 5 |       | eraction avec la lumière                                                       | 26 |

|   | 5.1   | Photopiles                                                                     | 26 |

|   | 5.2   | Photodiodes                                                                    | 27 |

| _ | ~ •   |                                                                                | •  |

| 6 | Crit  | tères de choix d'une diode.                                                    | 30 |

| 7 | Trai  | nsistors                                                                       | 30 |

| • | 7.1   | Qu'est ce qu'un transistor?                                                    | 30 |

|   | 7.2   | Utilisation                                                                    | 30 |

|   | 1.2   | Cunsation                                                                      | 50 |

| 8 | Trai  | nsistors à effet de champ                                                      | 30 |

|   | 8.1   | MOS canal N (NMOS)                                                             | 31 |

|   | 8.2   | MOS canal P (PMOS)                                                             | 32 |

|   | 8.3   | Caractéristiques statiques des transistors NMOS, modèle de Schichman et Hodges | 34 |

|   | -     | 8.3.1 Courant de grille                                                        | 34 |

|   |       | 8.3.2 Courant drain-source                                                     | 34 |

|   | 8.4   | Validité du modèle                                                             | 37 |

|   |       | 8.4.1 Paramètres d'influences                                                  | 37 |

|   | 8 5   | Stratégies de calcul : schémas équivalents                                     |    |

|   | 0.0   |                                                                                | 2) |

|    | 8.6  | Caract    | éristique statique des transistors PMOS                                                                                      | 39 |

|----|------|-----------|------------------------------------------------------------------------------------------------------------------------------|----|

|    |      | 8.6.1     | Mises en œuvre comparées des transistors NMOS et PMOS                                                                        | 40 |

|    | 8.7  | Transis   | stors MOS à apauvrissement                                                                                                   | 41 |

| 9  | App  | lications | s des transistors MOS                                                                                                        | 41 |

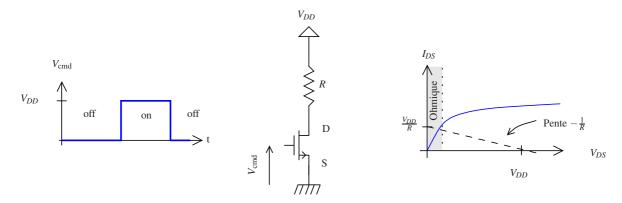

|    | 9.1  | MOS e     | n Commutation                                                                                                                | 41 |

|    |      | 9.1.1     | NMOS en pull-down                                                                                                            | 42 |

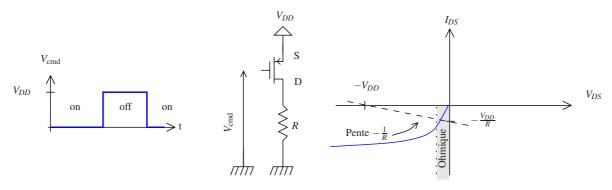

|    |      | 9.1.2     | PMOS en pull-up                                                                                                              | 42 |

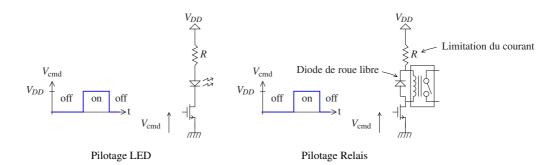

|    |      | 9.1.3     | Exemples d'application d'un NMOS en pull-down. : Pilotage d'une LED ou d'un relais par une porte                             |    |

|    |      |           | $logique. \dots \dots$ | 42 |

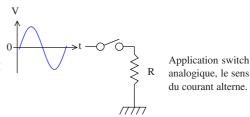

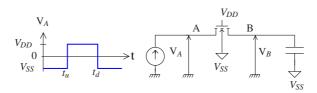

|    | 9.2  | Interru   | upteurs analogiques (Analog switches)                                                                                        | 43 |

|    | 9.3  | Portes    | logiques CMOS                                                                                                                | 46 |

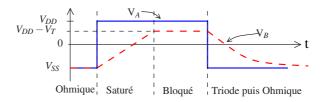

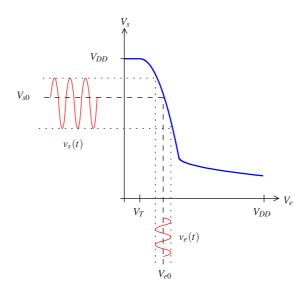

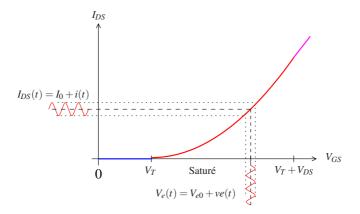

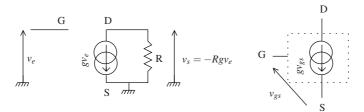

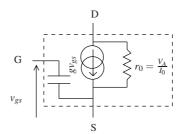

|    |      | 9.3.1     | L'inverseur MOS                                                                                                              | 46 |

|    |      | 9.3.2     | Quelques autres portes CMOS                                                                                                  | 47 |

|    | 9.4  | MOS e     | n Amplification                                                                                                              | 48 |

|    |      | 9.4.1     | Petit signal                                                                                                                 | 49 |

|    |      | 9.4.2     | Schéma équivalent petit signal                                                                                               | 49 |

|    |      | 9.4.3     | Méthodologie d'analyse du fonctionnement en petit signal d'un amplificateur à MOS                                            | 51 |

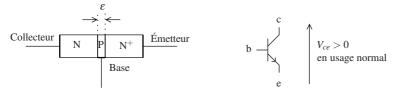

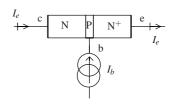

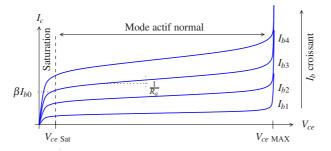

| 10 | Tran | sistors   | bipolaires à jonction                                                                                                        | 53 |

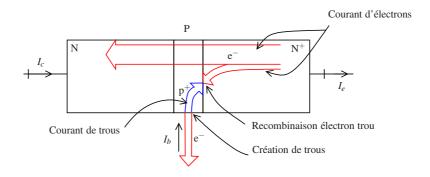

|    | 10.1 | Fonctio   | onnement                                                                                                                     | 53 |

|    | 10.2 | Caract    | éristiques                                                                                                                   | 54 |

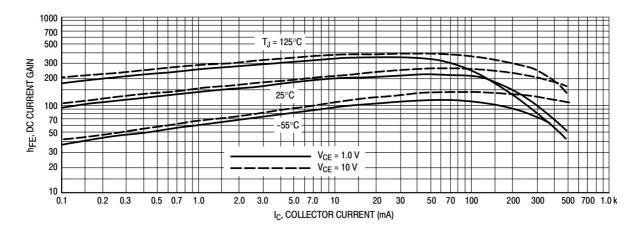

|    | 10.3 | Param     | ètres d'influences                                                                                                           | 56 |

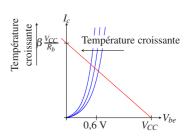

|    |      | 10.3.1    | Effet de la Température                                                                                                      | 56 |

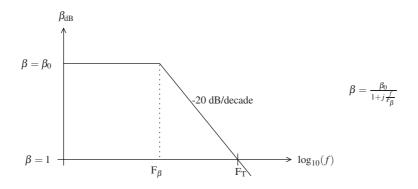

|    |      | 10.3.2    | Variation de $\beta$ avec la fréquence                                                                                       | 56 |

| 11 | App  | lications | s des transistors à jonction                                                                                                 | 57 |

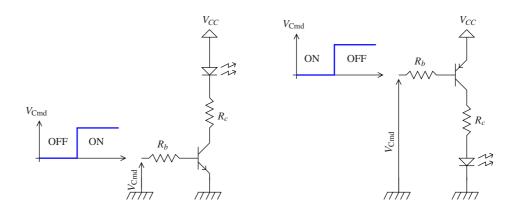

|    | 11.1 | BJT en    | Commutation                                                                                                                  | 57 |

|    | 11.2 | BJT en    | Amplification                                                                                                                | 58 |

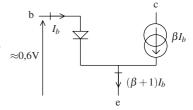

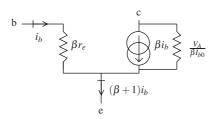

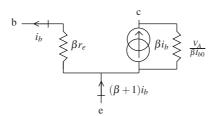

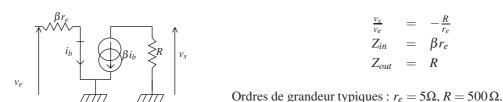

|    |      | 11.2.1    | Schéma équivalent petit signal                                                                                               | 58 |

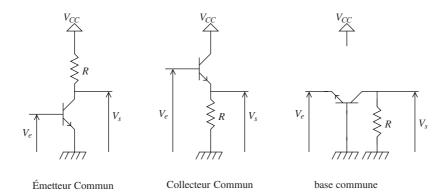

|    |      | 11.2.2    | Les trois montages de base des transistors bipolaires                                                                        | 59 |

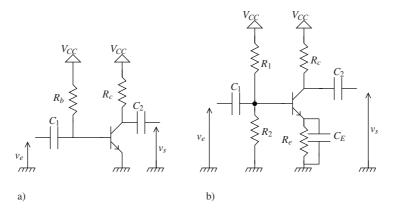

|    |      | 11.2.3    | Polarisation et emballement Thermique                                                                                        | 61 |

|    |      | 11.2.4    | Mise en œuvre d'un montage à émetteur commun, montage Cascode                                                                | 62 |

## 1 Semi-conducteurs

De façon simplifiée, un conducteur est un matériau qui conduit l'électricité grâce à la présence de charges ou porteurs de charges mobiles en son sein. Dans les solides ces charges sont en général des électrons. Les isolants quant à eux sont des matériaux dans lesquels les charges ou porteurs de charges sont très rares ou inexistants.

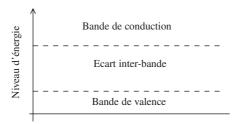

#### 1.1 Bases élémentaires de la théorie des bandes

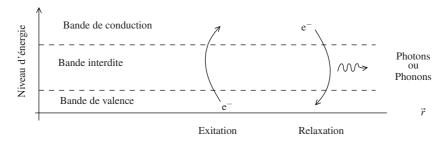

Dans un conducteur solide, à cause de l'interaction entre les atomes, il peut apparaitre un niveau d'énergie quantifié au dessus du niveau d'énergie des orbitales de chaque atome dans lequel les électrons peuvent se déplacer. C'est la bande de conduction présentée figure 1. Cette bande est séparée de la bande de valence par une bande interdite. La bande de valence résulte de la mise en commun d'électrons périphériques dans les liaisons covalentes. L'existence et la taille de la bande interdite dépend du ou des matériaux constituants le solide, de sa structure (amorphe ou cristallin) et de sa température.

FIGURE 1 – Bandes d'énergie dans un solide

La bande de conduction existe toujours pour les conducteurs. Pour les isolants, cette bande de conduction n'existe pas. Un semi-conducteur présente la même structure de bande qu'un conducteur, à ceci près qu'à basse température (0°K) la bande de conduction est vide. Elle se peuple avec la température. Un semi-conducteur est donc plus ou moins conducteur en fonction de la température.

# 1.2 Principaux semi-conducteurs utilisés en électronique

Les semi-conducteurs utilisés en électronique sont des mono-cristaux fabriqués artificiellement grâce à une technique de croissance appelée épitaxie. Ce sont principalement des mono-critaux de :

- Silicium, pour la très grande majorité des applications,

- Germanium, semi-conducteur historique dont l'usage a été abandonné,

- AsGa (Arsenure de galium), très utilisé pour les applications en micro ondes (fréquences de l'ordre de 1 à 100 GHz).

#### 1.2.1 Exemple du silicium.

| Couche       | K   | L   | M   |

|--------------|-----|-----|-----|

| Nb électrons | 2/2 | 8/8 | 4/8 |

Numéro atomique Z = 14. Les électrons sont donc répartis de la façon suivante :

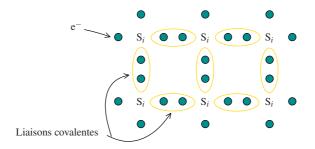

Il y a donc 4 électrons dans la bande de valence. La figure suivante présente la structure en terme de liaisons covalentes d'un cristal de silicium à très basse température.

Cette figure montre la répartition des électrons dans la bande de valence. Il n'y a pas, à cette température, d'électron dans la bande de conduction.

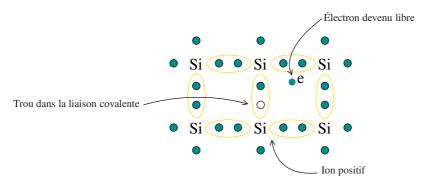

Lorsque la température s'élève (température ambiante), certaines des liaisons covalentes sont cassées par l'agitation thermique et certains électrons passent dans la bande de conduction. On a alors, comme représenté dans la figure ci dessous, libération d'un électron. Ce dernier vient peupler la bande de conduction et il y a apparition d'un ion positif de Silicium et d'un trou dans la liaison covalente cassée.

Ce phénomène est proportionnellement nombre d'atomes peu important, Il est de l'ordre de 3 pour 10<sup>13</sup> liaisons à 300 °K. Il est néanmoins suffisant pour que le silicium devienne conducteur, même si il reste un mauvais conducteur :

|   | Silicium | $2,5210^{-4}\mathrm{S/m}$ |

|---|----------|---------------------------|

| Ī | Cuivre   | 59,610 <sup>6</sup> S/m   |

Ce type de semi-conducteur naturel est dit semi-conducteur intrinsèque.

#### 1.2.2 Conduction par trous

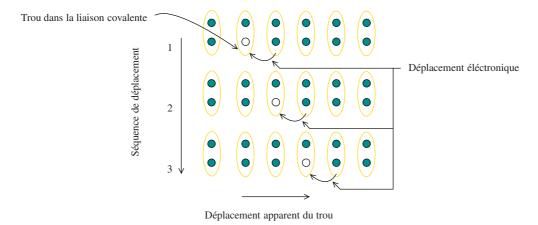

Il est très important de noter que le trou créé lors de la rupture de la liaison covalente participe lui aussi à la conduction. Les électrons encore liés aux atomes (les électrons dans la bande de valence) peuvent en effet changer d'atome comme présenté figure 2

FIGURE 2 – Déplacement d'un trou.

Les électrons de valence sont cependant bien plus liés à leur atome que les électrons de la bande de conduction. En conséquence la mobilité des trous est bien plus faible que celle des électrons de conduction. L'équation 1 permet de définir la mobilité des porteurs de charge.

$$V_{(m/s)} = \mu E \tag{1}$$

Dans cette équation, E est le module du champ électrique vu par le porteur de charge,  $\mu$  sa mobilité et V sa vitesse d'équilibre, conséquence du champ électrique. On voit ainsi que les mobilités s'expriment par exemple en m<sup>2</sup>V <sup>-1</sup>s<sup>-1</sup>.

Les valeurs des mobilités des trous et des électrons sont les suivantes :

| Électrons | $1500 \text{ cm}^2/\text{Vs}$ |

|-----------|-------------------------------|

| Trous     | $475 \text{ cm}^2/\text{Vs}$  |

Finalement, on peut retenir que la mobilité des électrons est environ trois fois plus grande que celle des trous :

$$\mu_{e^-} \approx 3 \times \mu_{\text{Trous}}$$

(2)

#### 1.2.3 Recombinaisons électrons-trous

Lorsqu'un électron libre rencontre un trou, il a évidement tendance à reprendre la place libre qui correspond à un niveau d'énergie plus faible. Ce phénomène spontané est un phénomène de relaxation appelé recombinaison électrontrou. La différence d'énergie est convertie selon le semi-conducteur soit en phonon (vibrations du réseau cristallin) soit en photon comme présenté dans la figure ci-dessous. En ce qui concerne le silicium compte tenu des niveaux d'énergie mis en jeu, c'est en phonons. Il n'existe en effet pas de LED (Diodes Électroluminescence) en silicium.

La création des paires électron-trou et la recombinaison sont deux phénomènes concurrents qui s'équilibrent à une valeur qui dépend de la température.

# 1.3 Dopages

En considérant l'exemple du silicium, on voit qu'une liaison covalente cassée donne lieu à  $\,\longmapsto\,$ un électron libre . un ion positif

Le dopage consiste à favoriser la création de trous ou d'électrons libres en insérant de façon contrôlée dans la maille cristalline des ions positifs ou négatifs qui constituent des impuretés vis à vis du cristal.

Pour le silicium : Ions + (Bore, 3e – de valence) création d'un trou Dopage p Ions - (Phosphore,  $5 e^-$  de valence)  $\implies$  création d'un électron libre Dopage n

Le taux d'impureté doit être contrôlé très précisément lors de l'épitaxie du cristal car la concentration de porteurs (trous ou électrons) en dépend. On créé ainsi des semi-conducteurs plus ou moins dopés : p, p<sup>+</sup>,p<sup>++</sup> ou n, n<sup>+</sup>,n<sup>++</sup>.

Les semi-conducteurs à dopage créés par impureté sont dit extrinsèques.

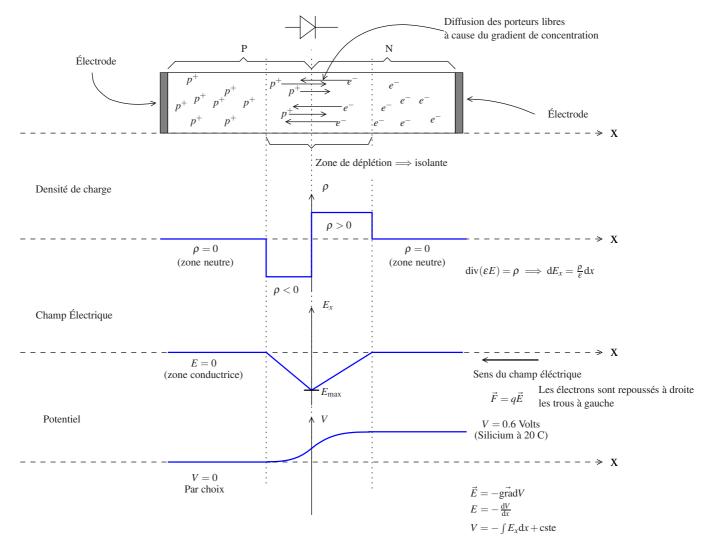

# La jonction PN

On crée une jonction dite "métallurgique" entre un barreau de semi-conducteur N (dopé n) et un autre dopé p (semiconducteur P). Jonction "métallurgique" (analogie avec la soudure ?) signifie qu'il ne s'agit pas d'un simple contact entre deux matériaux ce qui pourrait créer des barrières de potentiels, mais que l'on a un cristal continu dont le dopage change à la jonction.

À la jonction, les électrons majoritaires dans la zone N ont tendance à diffuser vers la zone P, et les trous de la zone P vers les zones N à cause du gradient de concentration de chacune des espèces de porteurs. Cela crée une zone de déplétion

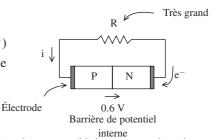

FIGURE 3 – Modèle simplifié de la jonction PN en circuit ouvert.

isolante comme présenté figure 3. On peut remarquer que les mobilités des trous et des électrons n'étant pas les mêmes, la zone de déplétion n'est pas symétrique.

La jonction présente alors un profil de densité de charge selon son axe x tel que celui représenté dans cette même figure. Il est alors possible de calculer le champ électrique résultant. En prenant le potentiel V nul pour l'électrode de la zone P, on en déduit la courbe de potentiel présentée. On voit qu'il apparait dans la jonction une barrière de potentiel. Cette dernière vaut 0.6 Volts à  $20^{\circ}$ C pour le silicium avec les valeurs de dopage usuelles.

# 2.1 Écrantage

Nous venons de voir que la diode présente une barrière de potentiel interne. Pourtant, si l'on mesure le potentiel au bornes d'une jonction avec le dispositif de droite par exemple :

On mesure un potentiel nul.

Ceci est dû à l'écrantage du potentiel par les charges libres ( $p^+$ et  $e^-$ ) présentes dans la jonction PN qui se déplacent pour venir rééquilibrer le potentiel.

La résistance R est celle du voltmètre. Elle est grande, néanmoins les charges se déplacent tout de même pour venir équilibrer (écranter) le potentiel interne. Lorsque le régime statique est atteint, i = 0, et l'on mesure un potentiel nul au bornes de la jonction.

**ATTENTION :** Cet écrantage n'annule pas les gradients de concentrations de porteurs internes. La densité de charge globale est nulle, mais les gradients ne le sont pas.

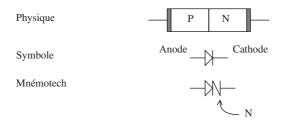

# 2.2 La jonction PN comme composant électronique : La diode

Le dipôle formé par une jonction PN est une diode. La figure 4 présente son symbole ainsi qu'un moyen mnémotechnique pour se souvenir de son orientation. Le trait de la cathode peut être complété pour former un N qui localise la position du dopage n.

FIGURE 4 – La jonction PN réalise une diode.

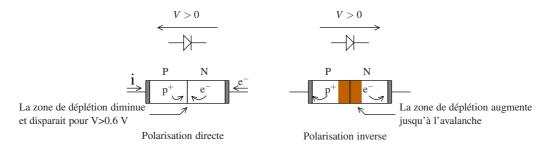

À cause de la zone de déplétion à la jonction, la diode ne conduit pas le courant. Pour que des électrons puissent traverser la diode, il leur faut vaincre la barrière de potentiel interne. Le comportement de la diode va être différent selon qu'on la polarise en direct, c'est-à-dire avec une différence de potentiel qui s'oppose à la barrière de potentiel, où en inverse, c'est-à-dire avec une tension qui renforce cette barrière. Ces deux modes de polarisation reviennent respectivement à diminuer jusqu'à annuler la zone de déplétion ou à agrandir cette même zone.

FIGURE 5 – Polarisation directe et indirecte de la diode.

**Remarque 1:** Même avec une zone de déplétion augmentée en polarisation inverse, la diode conduit un peu. Le courant vaut typiquement quelques dizaines de nA (25 nA pour la 1N4148). Cette conduction est due aux porteurs minoritaires qui restent présents dans la jonction : les électrons dans la zone P, les trous dans la zone N.

Remarque 2: Lorsque la tension augmente en polarisation inverse, le champ électrique dans la zone de déplétion augmente. Les électrons minoritaires de la zone P prennent de la vitesse. Lorsque le potentiel au bornes de la diode atteint une certaine valeur limite  $V_Z$  qui dépend du dopage, il y avalanche. Les électrons franchissant la zone de déplétion ont assez d'énergie pour décrocher certains de ceux engagés dans les liaisons covalentes, qui eux mêmes en décrochent d'autres. La résistance de la jonction s'écroule.

Cette tension s'appelle la tension Zener. Elle est grande devant 0.6 V pour les diodes classiques (≈20 V pour la 1N4148). Elle est contrôlée et spécifiée pour les diodes dites Zeners.

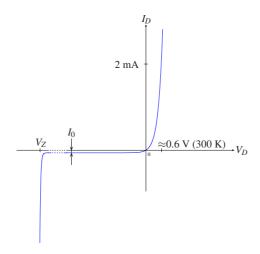

#### 2.3 Caractéristique statique courant/tension de la diode

La physique du solide permet, avec les considérations qualitatives précédentes, d'établir la caractéristique analytique de la diode. C'est l'équation 3 dite d'Ebers-Moll :

$$I_D \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad I_D = I_0(e^{\frac{V_D}{V_{\phi}}} - 1) \tag{3}$$

Dans cette équation  $I_D$  est le courant qui traverse la diode,  $V_D$  est la tension appliquée aux bornes de la diode,  $I_o$  est le courant résiduel lorsqu'elle est polarisée en inverse, et  $V_\phi$  la tension thermique. Cette équation ne décrit cependant pas le comportement en avalanche de la diode.

$V_{\phi}$  la tension thermique est donnée par l'équation 4

$$V_{\phi} = \frac{kT}{q} \tag{4}$$

Dans cette expression :

$$\begin{cases} & \text{k est la constante de Boltzman} & \text{k} = 1,38\ 10^{-}23\ \text{J/K} \\ & \text{T est la température en Kelvin} & & \text{T}_{\textit{K}} = \text{T}_{^{\circ}\text{C}} + 273.15 \\ & \text{q est la charge de l'électron} & & \text{q} = 1,6\ 10^{-19}\ \text{C} \end{cases} .$$

Pour fixer les idées, le tableau suivant donne les valeurs de la tension thermique pour quelques valeurs de la température :

| T °C | $V_{\phi}$ mV |

|------|---------------|

| 20   | 25,3          |

| 25   | 25,7          |

| 30   | 26,1          |

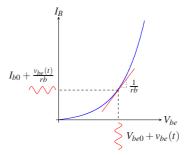

La variation est, compte tenu de l'équation 4, linéaire avec la température avec une pente de  $\frac{k}{q} = 0.086 \, \text{mV/°K}$ . La caractéristique courant tension pour la diode 1N4148 à 300°K est présentée figure 6.

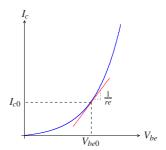

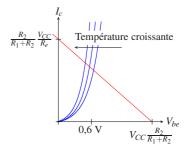

La caractéristique de la diode dépend de la température au travers du coefficient de tension thermique  $V_{\phi}$ . Comme  $V_{\phi}$  augmente avec la température,  $I_D$  devrait diminuer. La caractéristique devrait se déplacer vers la droite avec la température. Cependant, le courant inverse  $I_0$  dépend aussi de T comme présenté figure 5, où A est un coefficient qui dépend de la diode

FIGURE 6 – Caractéristique courant tension de la diode 1N4148 à 300°K.

(matériau et dopage).

$$I_0 = AT^3 (5)$$

L'effet de la variation de  $I_0$  avec la température sur  $I_D$  est prépondérant sur celui de la variation de  $V_{\phi}$  avec la température ;  $I_D$  augmente avec T. La caractéristique devrait se déplacer vers la gauche avec la température.

Variation avec la température : Considérons le montage suivant :

On peut exprimer  $V_D: V_D = E - RI_D$ .

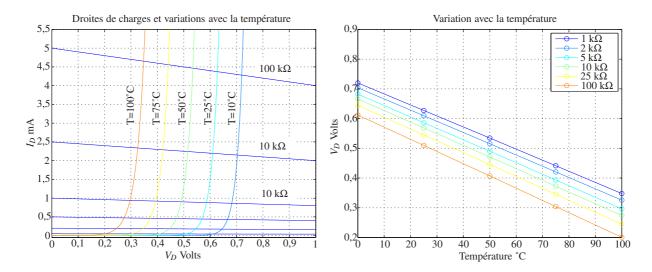

Cela permet de tracer les droites de charge (CF section 3.2) de la figure 7-gauche pour les variations de la caractéristique de la diode avec la température. Ces courbes ont été tracées pour  $E=5\mathrm{V}$ .

A partir de ce jeu de droites de charge on peut, pour chaque valeur de la résistance, en déduire la tension aux bornes de la diode en fonction de la température (figure 7-droite).

On remarque que toutes ces courbes présentent à peu près la même pente. On retrouve alors les valeurs classiquement admises dans la littérature :

$$V_D \approx 0.6 \,\mathrm{V}$$

$\frac{\mathrm{d}V_D}{\mathrm{d}T} = -2 \,\mathrm{mV/^{\circ}C}$

$V_D = 0.6 \,\mathrm{V}$  est la valeur classique dans la littérature francophone pour les diodes en conduction. La littérature Anglosaxonne utilise elle plutôt la valeur de 0,7 V. Il fait sans doute plus froid en Angleterre. Cette tension est souvent appelée tension de seuil de la diode.

# 3 Utilisation des diodes

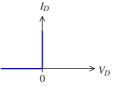

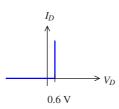

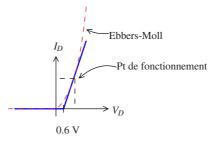

La caractéristique réelle de la diode telle que présentée figure 6 est compliquée. On utilise, dès que possible, une des trois caractéristique simplifiée de la diode :

1. Cas des grands signaux : les tensions mises en œuvres sont grandes devant 0,6 V.

FIGURE 7 – Variation de la tension au borne d'une diode avec la température.

Dans ce cas on peut souvent négliger la tension de seuil, on utilise la caractéristique simplifiée suivante, dite de la diode idéale :

2. Signaux plus petits : on ne peut alors négliger la tension de seuil. On utilise le modèle de la diode idéale à seuil :

3. Cas des petites variations : si les variations de tensions sont faibles et situées dans la zone du coude de la diode, les modèles précédents ne donnent en général pas le bon résultat. Il est possible d'affiner en utilisant le modèle de la diode avec résistance différentielle. La valeur de la résistance différentielle est alors calculée en dérivant l'équation d'Ebbers-Moll pour obtenir la pente ad-hoc autour du point de fonctionnement considéré.

4. Si aucun des modèles précédents ne convient, on utilise le modèle d'Ebbers-Moll de l'équation 3. Dans tous les cas, on utilise le modèle le plus simple possible qui permet d'établir les bons résultats. Le bon résultat est celui qui correspond à ce que l'on peut réaliser et mesurer.

Retenons que:

ON UTILISE TOUJOURS LE MODÈLE LE PLUS SIMPLE POSSIBLE

# 3.1 Stratégies de calcul

La difficulté dans un circuit comportant des diodes consiste à trouver le bon angle d'attaque.

Il est souvent commode de raisonner en courant.

Avec le modèle de la diode idéale à seuil :

— Hypothèse 1 :

$$I_D=0$$

; Diode Bloquée On calcule  $V_D$  Si  $V_D<0,6$  V  $\longrightarrow$  Hypothèse vérifiée — Hypothèse 2 :  $I_D\neq 0$  ; Diode passante  $\Longleftrightarrow V_D=0,6$  V On calcule  $I_D$  Si  $I_D>0$   $\longrightarrow$  Hypothèse vérifiée

L'hypothèse diode bloquée ou passante est bien sûr guidée par le fait que le courant ne peut circuler que de l'anode vers la cathode dans la diode.

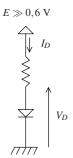

#### Exemple 1

$E \gg 0.6 \text{ V}$   $\downarrow I_D = (E - 0.6)/V$   $\downarrow V_D = 0.6 V$

L'hypothèse naturelle ici est diode passante. En effet avec E>0 le courant ne peut circuler que du haut vers le bas.

Cette hypothèse amène à  $I_D = (E - 0.6)/R$ . Comme  $I_D > 0$  l'hypothèse est vérifiée.

L'hypothèse diode bloquée donnerait  $V_D = E$ , ce qui invaliderait l'hypothèse.

Sens direct

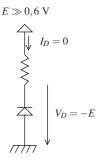

# Exemple 2

L'hypothèse naturelle ici est diode bloquée. La diode ne peut ici laisser circuler le courant que du bas vers le haut.

Cette hypothèse amène à  $V_D = -E$ . Comme  $V_D < 0.6$  V, l'hypothèse est vérifiée.

L'hypothèse diode passante donnerait  $I_D = -(E+0.6)/R$ . Dans ce cas  $I_D < 0$  ce qui invaliderait l'hypothèse.

Sens inverse

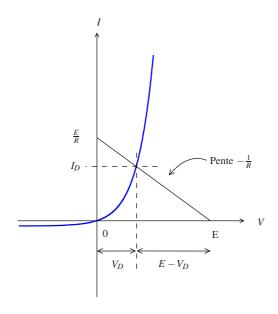

# 3.2 Droite de charge

Il est essentiel de savoir tracer les droites de charges pour prévoir le comportement de nombreux circuits non linéaires et diriger les raisonnements. Ce n'est pas un gadget, il faut savoir les tracer et penser à les utiliser.

Exemple: Tracé de la droite de charge correspondant au comportement en température de la section 2.3.

On calcule  $V_D$

$$V_D = E - RI_D$$

On peut alors exprimer  $I_D$ :

$$I_D = -\frac{1}{R}V_D + \frac{E}{R}$$

On voit que c'est l'équation d'une droite de pente  $-\frac{1}{R}$  qui intercepte l'axe des ordonnées en  $\frac{E}{R}$ , et l'axe des abscisses en E. On trace alors facilement la droite de charge comme présenté ci-dessous. Le résultat est obtenu ici avec le modèle d'Ebbers-Moll comme le permet le tracé de la droite de charge, et non avec le modèle de la diode idéale à seuil comme dans la section précédente.

Conseil: Pensez à tracer les droites de charge pour comprendre ce qui se passe, avant de vous lancer dans les calculs.

# 3.3 Montages de base

Ici suivent des exemples choisis pour leur utilité pratique ou pour les raisonnements mis en œuvre pour leur compréhension.

#### 3.3.1 Redressement simple alternance

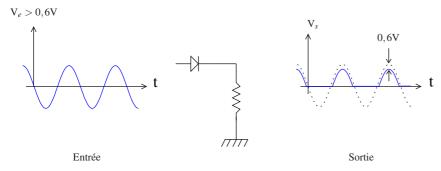

La diode coupe simplement l'alternance négative en ne laissant passer le courant que dans un sens. On peut remarquer sur la sortie l'effet de la tension de seuil. Le modèle utilisé ici est celui de la diode idéale à seuil.

#### 3.3.2 Redressement double alternance

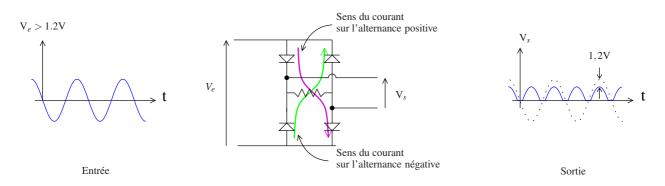

Le montage précédent ne permet pas de récupérer toute l'énergie du signal d'entrée, pour des applications d'alimentation par exemple. On lui adjoint une deuxième diode afin de permettre de récupérer les deux alternances. L'idée est de fournir au courant un chemin électrique qui lui permette de traverser la charge dans le même sens à chaque alternance. C'est le principe du pont en H.

Comme on peut le voir dans le schéma ci-dessus, le courant passe toujours dans le même sens dans la charge quelquesoit l'alternance. Ici encore, on peut remarquer sur la sortie l'effet de la tension de seuil. Le modèle utilisé ici est toujours celui de la diode idéale à seuil.

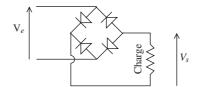

Le principe du pont en H est classique et est à retenir.

**Remarque 1 :** Ce montage ne fonctionne que chargé. En absence de la résistance,  $V_s$  n'est pas imposé par le circuit. **Remarque 2 :** Il est souvent représenté comme suit et doit être reconnu au premier coup d'œil.

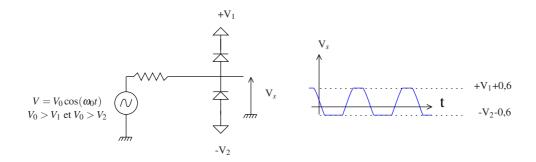

# 3.3.3 Écrêtage (clamping)

L'écrêtage est l'une des grandes utilisations des diodes. Il est souvent exploité pour protéger d'autres circuits en limitant leur tension d'entrée.

On peut avoir  $V_1 = V_2 = 0$ , dans ce cas l'excursion de sortie est limitée à  $\pm 0.6$  V. C'est le montage type de protection contre les surtensions des amplificateurs d'instrumentation où les signaux à amplifier sont en général très petits devant 0.6 V.

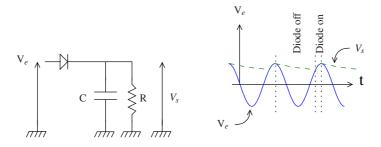

#### 3.3.4 Détection de crêtes

Le condensateur se charge sur les alternances positives au travers de la résistance différentielle de la diode qui est de l'ordre de la dizaine d'Ohm. Pendant les alternances négatives, la diode est bloquée et le condensateur se décharge dans la résistance avec la constante de temps  $\tau = RC$ .

En choisissant correctement  $\tau$ , ce circuit peut être typiquement appliqué à la démodulation d'amplitude. Si  $\tau$  est suffisamment grand, la tension de sortie peut être considérée comme constante et est égale à la valeur crête positive maximale atteinte.

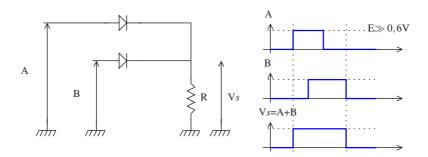

# 3.3.5 Logique à diodes

Dès que l'une des diodes est passante, la tension aux bornes de R vaut E (diode idéale  $E\gg 0,6$  V). La fonction logique réalisée est un OR (OU logique).

L'intérêt de ce montage n'est pas de remplacer une porte logique, mais réside dans ses niveaux de sortie. En fonction des diodes choisies, il permet de réaliser une porte OR supportant de grandes valeurs de courant et de tension .

#### 3.3.6 Diode de roue libre

Se reporter au chapitre alimentation à découpage.

#### 3.3.7 Pompe à diode

Ce circuit est un circuit très simple, mais dont le fonctionnement est très astucieux et assez compliqué si l'on rentre vraiment dans les détails.

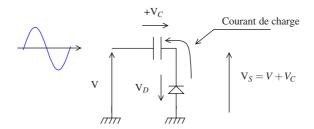

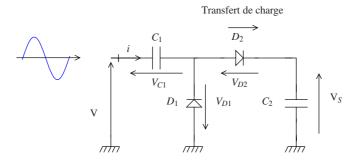

#### Premier étage : Pompage de la charge.

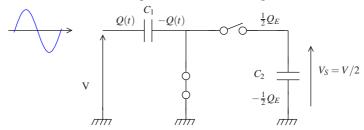

On utilise ici le modèle de la diode idéale. Le modèle de la diode à seuil pourrait être utilisé, c'est même nécessaire si l'amplitude du signal d'entrée V n'est pas beaucoup plus grande que 0,6 V. Les raisonnements sont les mêmes dans les deux cas. On se contentera du modèle le plus simple pour des raisons de clarté.

Le raisonnement en courant est ici, comme souvent avec les diodes, le plus efficace. Le condensateur ne peut se charger que si le courant est dans le sens indiqué sur la figure précédente. Pour cela, il faudra avoir  $V_D>0$ , c'est-à-dire une alternance négative.

Avec le condensateur initialement déchargé, donc  $V_C = 0$ ,  $V_D$  devient positif dès que V < 0. La diode devient passante et la tension de sortie est nulle. La diode reste passante jusqu'à ce que le sens du courant s'inverse, c'est-à-dire jusqu'à ce que la tension remonte  $(i = \frac{dV}{dT})$ . Ce fonctionnement est résumé dans la figure suivante.

On voit que l'on a bloqué la charge dans la diode ce qui conduit à un offset de la tension de sortie.

Retenons que la diode devient passante dès que la charge +Q sur l'électrode de droite du condensateur est inférieure à CV.

Deuxième étage : on rajoute un étage de stockage de la charge. L'étage rajouté ressemble à un détecteur de crête. De cette façon, on cherche à obtenir en sortie une tension constante égale à 2E. En pratique, c'est beaucoup moins simple car le fonctionnement de l'étage de pompage de charge est influencé par l'étage de transfert de charge. Néanmoins l'étage rajouté fonctionne sur le même principe que le détecteur de crête, c'est-à-dire en bloquant la charge dans le condensateur  $C_2$ . Dans ce montage les capacités des condensateurs  $C_1$  et  $C_2$  sont les mêmes.

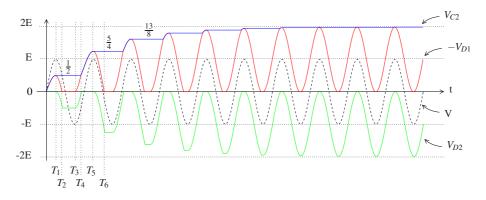

Les chronogrammes des différents signaux de la pompe à diode en fonctionnement sont représentés figure 8.

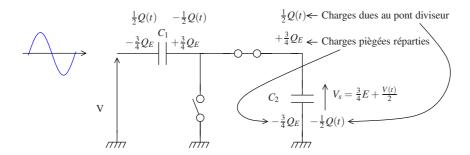

On suppose les condensateurs initialement déchargés. La tension d'entrée est  $V = E\cos(\omega t)$ . On pose Q(t) = CV(t) la charge stockée dans l'un ou l'autre des condensateurs quant la différence de potentiel vaut V(t) à leurs bornes et  $Q_E = CE$  la valeur de cette charge lorsque V(t) = E.

FIGURE 8 – Chronogrammes du doubleur de tension à pompe à diode

# Analyse du fonctionnement :

#### -- t = 0:

V=0, les deux condensateurs sont déchargés et  $V_{C1}=V_{C2}=0$ . Le courant dans chacune des diodes est nul, elles sont donc bloquées et  $V_S=0$ .

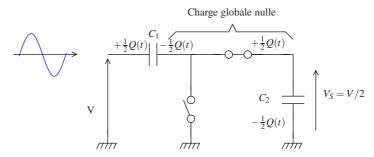

#### — t=0+:

La tension d'entrée V devient positive, ce qui demande un courant d'entrée positif.  $D_1$  reste bloquée et  $D_2$  devient passante :  $V_{D2} = 0$ .

Le schéma équivalent du montage est donc :

Comme  $D_1$  est bloquée, la charge globale entre les deux condensateurs est nulle et se répartit comme dans la figure ci-dessus avec  $V_s = V/2$  (pont diviseur capacitif).

De plus

$$V_{C1} = V - \frac{V}{2} = \frac{V}{2}$$

et  $V_{D1} = -V_S = -\frac{V}{2}$ .

#### $- t = T_1$

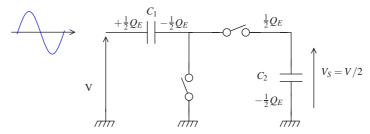

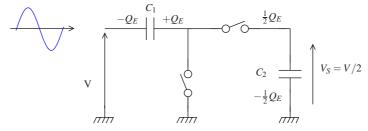

Dès que la tension en entrée V diminue, la diode  $D_2$  se bloque car le courant tend à s'inverser pour décharger  $C_2$  au travers de  $D_2$  pour suivre la tension V(t). Les deux diodes sont bloquées et le schéma équivalent devient :

La charge piégée dans  $C_2$  vaut  $Q_E/2$  et la tension de sortie reste constante et vaut :  $V_S = E/2$ .

La charge piégée dans  $C_1$  vaut  $-Q_E/2$  et  $V_{D1}=-(V-E/2)=E/2-V$ . La diode  $D_1$  restera bloquée tant que  $V_{D1}<0$

$-t = T_2$

$V(T_2) = E/2 \Longrightarrow V_{D1} = 0$ . La diode  $D_1$  redevient passante. Le schéma équivalent devient :

La charge dans  $C_1$  recommence à suivre la tension V(t).  $C_1$  se charge jusqu'à ce que V(t) atteigne sa valeur minimale -E, soit une charge  $+Q_E$  sur l'électrode de droite de  $C_1$  (V(t) < 0).

$- t = T_3$

$D_1$  se bloque car les charges ont maintenant tendance à quitter  $C_1$ .  $D_1$  et  $D_2$  sont bloquées :

$V_{C1} = E$ .

$V_S$  reste constante.

$-- t = T_4$

$D_2$  redevient passante dès que V(t) est suffisamment grande pour recommencer à charger  $C_2$ , c'est-à-dire lorsque  $V(t) + E = \frac{E}{2}$ , soit en  $V(T_4) = -\frac{E}{2}$ :

Les charges sur les électrodes internes des deux condensateurs (électrode de gauche de  $C_1$  et électrode de droite de  $C_2$ ) sont la somme des charges précédemment piégées, qui se répartissent équitablement  $\left(+\frac{1}{2} \times \frac{3}{2} Q_E\right)$ , et de la répartition de charges dues au pont diviseur capacitif qui est de nouveau actif  $\left(\pm \frac{Q(t)}{2}\right)$ . On a donc :  $V_s = \frac{3}{4}E + \frac{V(t)}{2}$ .

$-- t = T_5$

$D_2$  se bloque comme dans l'alternance précédente lorsque V(t) diminue pour prévenir la fuite des charges de  $C_2$ . Le schéma équivalent devient :

Compte tenu de la répartition des charges et de la valeur de  $V(T_5)$ :  $V_s = \frac{3}{4}E + \frac{1}{2}E = \frac{5}{4}E$ .  $V_s$  reste constante jusqu'à ce que  $D_1$  se débloque. Comme la charge bloquée dans  $C_1$  vaut  $\frac{1}{4}Q_E$ , la diode  $D_1$  se débloquera dès que  $V(t) + \frac{1}{4}E = 0$ .

—

$$t = T_6$$

$V(T_6) = -\frac{1}{4}E \Longrightarrow D_1$  redevient passante. On a :  $V_{D_1} = 0$ .

Elle se re-bloquera comme précédemment au minimum de l'alternance de V(t) et ainsi de suite.

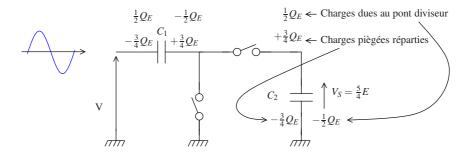

**Conclusion** A chaque nouveau blocage de  $D_1$ , la charge stockée dans  $C_2$  s'ajoute à la charge  $+Q_E$  pompée dans  $C_1$  lors de la phase de conduction de  $D_1$ . Cette charge se répartit et s'ajoute à celle du pont diviseur lorsque  $D_2$  redevient passante. On aboutit à la récurrence suivante :

$$Q_{0} = 0$$

$$Q_{1} = \frac{1}{2}Q_{E}$$

$$Q_{2} = (Q_{1} + Q_{E})\frac{1}{2} + \frac{1}{2}Q_{E} = \frac{1}{2}Q_{1} + Q_{E} = \frac{5}{4}Q_{E}$$

$$Q_{3} = \frac{1}{2}Q_{2} + Q_{E} = \frac{13}{8}Q_{E}$$

$$\vdots$$

$$Q_{i} = \frac{1}{2}Q_{i-1} + Q_{E}$$

(6)

Il s'agit d'une suite arithmético-géométrique que l'on peut résoudre :

$$Q_{n>0} = Q_E \left[ \frac{2^{n+2} - 3}{2^{n+1}} \right] \tag{7}$$

Quant  $n \to +\infty$  La charge tend vers  $2Q_E$  et  $V_S$  vers 2E ce qui était le but recherché.

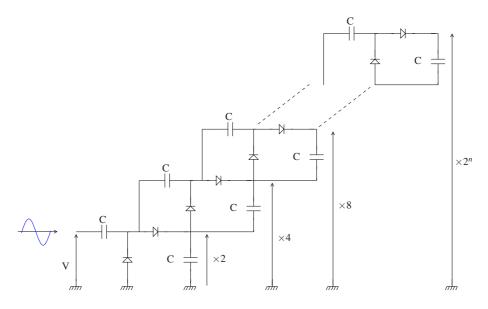

**Généralisation** En considérant la figure 9, on peut voir que le potentiel sur l'anode de  $D_2$  (électrode de gauche) est de la forme  $E + \cos(\omega t)$ . L'idée vient naturellement de charger le doubleur par un autre doubleur et ainsi de suite. On obtient ainsi le montage de la figure 9.

Là encore l'analyse précise du fonctionnement n'est pas triviale. On peut vérifier cependant qu'une pompe à n étages permet de récupérer l'amplitude de la sinusoïde d'entrée multipliée par  $2^n$ .

Les résultats obtenus avec le doubleur de tension montrent que la tension finale n'est pas atteinte, les diodes  $D_1$  et  $D_2$  sont alternativement, en opposition de phase, bloquées et passantes.

Ce résultat se généralise aisément à une pompe à *n* étages en considérant le sens du courant demandé par le générateur. C'est ce fonctionnement qui vaut son nom à ce montage.

FIGURE 9 – Pompe à diode à n étages.

**Applications** La pompe à diode permet d'obtenir facilement de très hautes tensions (quelques centaines de kV). Le courant disponible en sortie est cependant très faible car il dépend de l'efficacité du pompage qui diminue avec la tension. En effet lorsque la tension de sortie est nulle on transfère une charge  $Q_E/2$  à chaque alternance. Cependant, au niveau de charge correspondant à la énième itération le transfert de charge n'est plus que de  $\frac{3}{2n+1}$ .

Ce montage reste cependant le montage de choix dans les applications qui demandent de très hautes tensions avec très peu de courant tel que les compteurs Geiger et pour la polarisation des diélectriques par exemple.

Il reste aussi un très bon exercice de compréhension du fonctionnement d'un montage à diodes.

# 4 Autres types de diodes

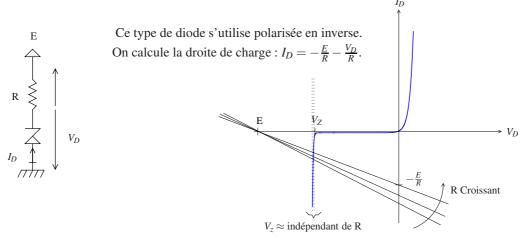

# 4.1 Diodes Zener

Ce type de diode tire parti de l'effet Zener. La tension d'avalanche est fixée précisément à la construction en jouant sur l'épaisseur de la jonction et du dopage.

De cette façon, comme la pente de la zone d'avalanche sur la caractéristique est très raide et peu dépendante de la température, on obtient facilement une référence de tension.

Attention : Bien que le choix de la résistance n'influe pas sur la tension délivrée, il permet de contrôler le courant

dans la diode :  $I_D = \frac{E - V_Z}{R}$  . Ce dernier doit être compatible avec ce que peut supporter la diode en terme de dissipation thermique.

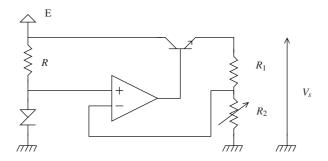

**Exemple d'application : référence de tension pilotable.** le problème avec le montage précédent est que l'on ne peut pas mettre n'importe quelle charge en sortie. Si on tire trop de courant, le diode peut quitter le mode d'avalanche en faisant descendre la tension  $V_D$  en dessous de  $V_Z$ . Le lecteur pourra le vérifier.

Le montage de la figure 10 permet de contourner le problème car le courant  $I^+$  reste toujours faible. C'est le transistor qui fournit le courant, la tension de sortie est simplement asservie sur la tension de la diode Zener en fonction de la valeur du pont diviseur. On obtient alors une référence de tension réglable avec une faible impédance de sortie : approximativement celle de l'alimentation en série avec la résistance passante du transistor.

FIGURE 10 – Référence de tension réglable à diode Zener.

On vérifie aisément que  $V_S = \frac{R_1 + R_2}{R_2} V_Z$ .

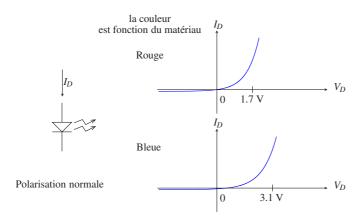

# 4.2 Diodes Électroluminescentes (LED)

Les diodes électroluminescentes (Light Emitting Diodes) émettent de la lumière lorsqu'elles sont traversées par un courant. On les polarise donc en direct.

L'émission de lumière est due à la désexcitation d'un électron qui retourne dans la bande de valence. C'est en fait une recombinaison électron-trou comme présenté au paragraphe 1.2.3.

L'énergie, donc la fréquence de la lumière, dépend du matériau utilisé. C'est aussi le cas de la tension de seuil.

**Remarque 1 :** Pour le silicium, le gap d'énergie entre la bande de valence et la bande de conduction interdit la création d'un photon, un phonon est créé à la place (vibration du réseau cristallin). Il n'existe pas de LED au silicium.

**Remarque 2 :** Il est aussi possible grâce à cette émission de lumière de créer des diodes laser (CF cours d'optique deuxième année).

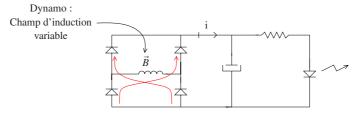

**Un exemple intéressant :** La figure 11 présente la mise en œuvre du pilotage d'une LED par une dynamo. Quel est le rôle de chacun des composants ?

FIGURE 11 – Exemple d'application : alimentation d'une LED par une dynamo.

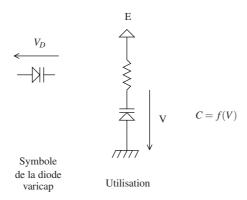

# 4.3 Varicaps

Comme présenté figure 5, la jonction PN présente une zone de déplétion lorsqu'elle est polarisée en inverse. Avec ses électrodes la zone de déplétion ainsi créée présente la structure d'un condensateur : Electrode-Isolant-Electrode. Comme l'épaisseur de la zone isolante (zone de déplétion) dépend de la tension aux bornes de la diode en polarisation inverse, on peut tirer parti de cet effet pour créer une capacité variable.

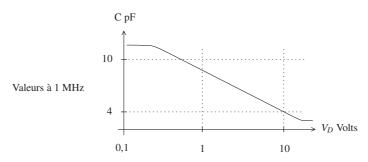

Certaines diodes comme la SOD 323 sont fabriquées pour exploiter cet effet. La figure 12 présente, à titre d'ordre de grandeur, les performances de cette dernière.

FIGURE 12 – Extrait des performances typiques SOD323.

Les varicaps sont typiquement utilisées dans le pilotage en tension d'oscillateurs.

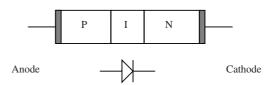

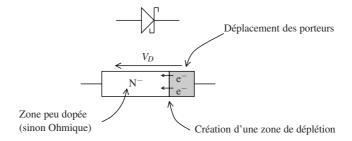

# 4.4 Diodes PIN

Les diodes PIN sont constituées de deux jonctions entre un semi-conducteur intrinsèque I, et deux semi-conducteurs extrinsèques respectivement dopés P et N comme présenté ci-dessous.

Le fonctionnement détaillé de ce type de diodes ne sera pas abordé ici.

#### Principales différences par rapport à une diode classique PN:

| Tension de seuil faible                                 | pprox 0.4  V                       |

|---------------------------------------------------------|------------------------------------|

| Tension de claquage élevée                              | >10 kV                             |

| Capacité propre faible et peu dépendante de la tension. | C'est tout l'inverse d'une varicap |

Ces diodes sont très utilisées en hyperfréquence comme interrupteur. En BF on les utilise surtout pour leur faible tension de seuil ou leur tension de claquage élevée.

# 4.5 Diodes Schottky

Les diodes Schottky (Schottky barrier diodes) sont constituées d'une jonction métal semi-conducteur :

La création d'une zone de déplétion crée, comme dans la jonction PN, une barrière de potentiel.

# Principales différences par rapport à une diode classique PN:

| Tension de seuil faible | $\approx 0.2 \text{ V}$      |

|-------------------------|------------------------------|

| Commutation très rapide | Moins de porteurs à déplacer |

| Courant inverse élevé   | qq μA                        |

Elle sont très utilisées en protection contre les surtensions à cause de leur rapidité.

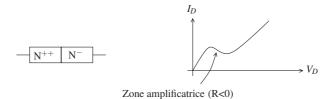

# 4.6 Diodes GUN (Hyperfréquences)

Leur usage est principalement limité aux hyperfréquences, où elles sont utilisées pour réaliser des oscillateurs en tirant parti de leur zone amplificatrice.

# 5 Interaction avec la lumière

Lorsqu'un photon provenant d'une source électromagnétique externe pénètre dans la zone de déplétion d'une jonction PN, il peut, si son énergie est suffisante, casser une liaison covalente et donc créer une paire électron-trou.

Pour le silicium, l'énergie minimale nécessaire pour le photon incident est de 1,1 eV. Cette condition peut s'exprimer comme :

$$hV > 1,1eV$$

(8)

h est la constante de Plank, v est la fréquence du photon considéré.

On peut en déduire la condition équivalente sur la longueur d'onde du photon :

$$\lambda < 1,3 \quad \mu m$$

(9)

On se trouve donc dans l'infra-rouge lointain. Les jonctions PN au silicium sont donc sensibles aux sources lumineuses à partir de l'infra-rouge.

A cause du champ électrique qui règne dans la zone de déplétion en circuit ouvert (CF figure 3), ou des gradients de concentration de porteurs de charge si on est en circuit fermé l'électron et le trou ainsi créés se déplacent en sens inverse l'un de l'autre sans se recombiner et cela se traduit par l'apparition d'un courant.

Les photopiles (cellules photovoltaïques) et les photodiodes utilisent ce phénomène respectivement pour la production d'énergie et la détection des photons. Les deux types de composant sont des jonctions PN que la lumière peut atteindre. Ils ne sont cependant pas optimisés dans le même but. Dans le premier cas, le rendement énergétique est visé, dans le deuxième cas c'est la sensibilité. Les deux composants ne s'utilisent pas non plus de la même façon.

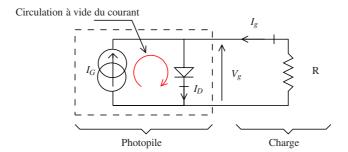

# 5.1 Photopiles

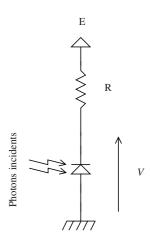

La photopile est une source de courant et s'utilise comme un générateur. Elle est simplement branchée sur une charge comme dans la figure ci-dessous. Son schéma équivalent comporte donc un générateur de courant. Il comporte aussi une diode qui modélise la caractéristique courant tension de la jonction PN. Comme la photopile peut être en circuit ouvert (non chargée) et que le courant généré circule, le générateur de courant et la diode du modèle doivent être orientés de façon ad-hoc.

Dans ce schéma,  $I_G$  est le courant généré par le flux  $\Phi$  de photons incidents sur la jonction :  $I_G = f(\Phi)$ . La diode qui modélise la jonction est traversée par le courant  $I_D$ . La tension  $V_D$  est aussi la tension fournie par le générateur  $V_g$ .  $V_g$  et  $I_D$  sont donc reliés par l'équation d'Ebbers-Moll (équation 3). Enfin  $I_g$  est le courant fourni à la charge.

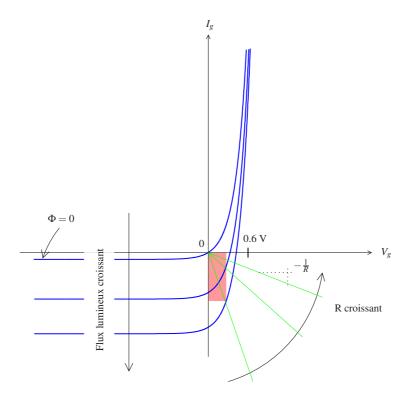

On peut alors tracer la caractéristique courant-tension de la photopile chargée  $I_g = f(V_g)$ .

$$I_g = I_D - I_G \tag{10}$$

Dans cette équation, seul  $I_D$  dépend de  $V_g$ . La caractéristique de la photopile en circuit ouvert est donc celle d'une diode décalée vers le bas de  $I_G$  comme présenté figure 13.

FIGURE 13 – Jeu de caractéristiques d'une photopile et droites de charges.

On peut alors tracer la droite de charge pour une charge résistive :  $V_g = -RI_g$ . On voit alors que compte tenu de la raideur de la caractéristique de la jonction PN, la tension aux bornes du générateur dépend peu de R et vaut approximativement 0,6 V pour une jonction au silicium. La meilleure valeur pour R est celle qui permet de récupérer le maximum de puissance, c'est-à-dire celle qui correspond à la plus grande surface du polygone (coloré)  $V_D \times I_D$  (sa pointe droite en bas se trouve alors a peu près dans le coude de la caractéristique) dans la figure 13. Soit pour une valeur de R optimale qui dépend de  $\Phi$ .

Il est possible, pour obtenir de plus grandes valeurs de tension, de cascader en série autant de photopiles que nécessaire. On obtient alors une tension de sortie multiple de 0,6 V.

#### 5.2 Photodiodes

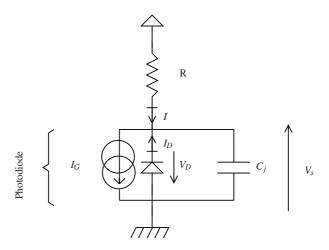

Alors que la photopile est utilisée comme un générateur et est polarisée en direct, la photodiode est utilisée comme un détecteur et est polarisée en inverse :

- 1. Chaque photon incident créé une paire électron trou.

- 2. Les électrons créés se déplacent sous l'action du champ électrique dû à la polarisation (E) et créent d'autres paires par collision avec ceux encore engagés dans des liaisons covalentes. Il en résulte une amplification du photocourant. Attention l'énergie est ici fournie par l'alimentation E.

- 3. La tension V, qui vaut E en l'absence de photons incidents, décroit rapidement.

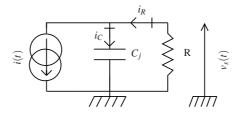

Schéma équivalent : le schéma équivalent est le même que celui de la photodiode. C'est en effet intrinsèquement le même composant. Cependant, comme on l'utilise en polarisation inverse, il faut tenir compte de la capacité de jonction  $C_j$ . Cette capacité à les mêmes origines que pour les varicaps (CF 4.3). On obtient donc le schéma équivalent suivant, dans lequel  $I_G$  est le photo courant multiplié.

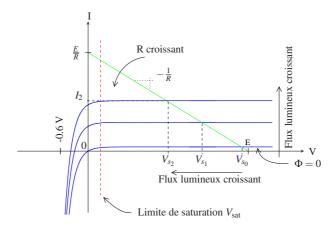

Sensibilité statique : Ici encore pour obtenir la sensibilité statique, il faut tracer la droite de charge :

$$V = -V_D = E - RI$$

$$I = I_G - I_D$$

(11)

On remarquera le signe moins devant la tension de la diode qui implique une symétrie de la caractéristique courant tension. Le tracé est présenté figure 14. Il permet de vérifier que la sensibilité augmente avec R. Il fait aussi apparaitre que le système sature dès que le flux de photons devient trop grand à cause du coude de la diode. La réponse de la photodiode ne sera pas linéaire dans cette zone. Cela se traduit par un tension minimale  $V_{\rm sat}$  en dessous de laquelle on ne peut descendre. Le bon choix pour R est donc un compromis entre saturation et sensibilité.

FIGURE 14 – Jeu de caractéristiques d'une photodiode et droite de charge.

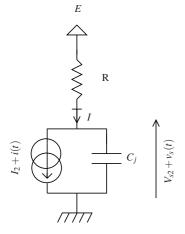

Sensibilité dynamique, limitation de la bande passante par la capacité de jonction. La photodiode est un détecteur. Le flux de photon en entrée peut être très rapidement variable (dans les applications d'alimentation avec les photopiles, le problème ne se pose pas).

Considérons un flux moyen de photons égal à  $\Phi_2$ , tel que en moyenne, on soit autour du point  $(Vs_2, I_2)$  de la figure 14. Si de plus les variations du flux de photons sont telles que l'on ne s'approche pas de la zone de saturation (la caractéristique de la diode reste plate dans la zone de travail), alors on peut simplifier le schéma équivalent comme suit :

Dans cette figure, le courant de photon a été décomposé entre sa valeur moyenne  $I_2$  et sa partie variable i(t). Il en résulte la décomposition équivalente du signal de sortie entre valeur moyenne  $V_{s_2}$  et partie variable v(t).

Par superposition, on étudie séparément la réponse à sa valeur moyenne et à sa partie variable.

La valeur moyenne  $I_2$  est un courant continu qui ne passe pas par le condensateur. Donc  $V_{s_2} = E - RI_2$ . Le schéma équivalent pour la valeur moyenne est donc le même schéma que celui de gauche sans le condensateur de jonction.

Le courant variable se divise entre la résistance et le condensateur :  $i(t) = i_R(t) + i_C(t)$ .

Avec  $V_{s_2} + v_s(t) = E - R(I_2 + i_R(t))$ , soit :

$$v_s(t) = -R.i_R(t) (12)$$

On obtient donc pour la partie variable le schéma équivalent qui suit :

Notez le sens du courant dans le schéma équivalent qui permet de tenir compte du signe dans l'équation 12. Ce schéma permet de calculer facilement la réponse à la partie variable du signal grâce au pont diviseur de courant :

$$i_R(\omega) = i(\omega) \frac{1/jC\omega}{1/jC\omega + R}$$

(13)

Soit compte tenu de l'équation 12 :

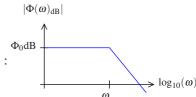

$$v_s(\omega) = -i(\omega) \frac{R}{1 + jRC\omega} \tag{14}$$

La capacité de jonction donne donc une fréquence de coupure à -3dB pour  $\omega = \frac{1}{RC}$

#### 6 Critères de choix d'une diode.

Lorsque l'on doit choisir une diode, les paramètres principaux à considérer sont les suivants :

| Nom                   | Description                                              | Valeur de référence (1N4148) |

|-----------------------|----------------------------------------------------------|------------------------------|

| Courant moyen         | Courant continu maximum que peut supporter la diode.     | 300 mA                       |

| Tension d'avalanche   | $V_Z$ tension Zener                                      | 75 V                         |

| Courant inverse       | $I_0$                                                    | 25 nA                        |

| Temps de recouvrement | Temps nécessaire pour passer de l'état bloqué à passant. | 8 ns                         |

| Capacité de jonction  | Valeur de la capacité en mode bloqué                     | 4 pF                         |

TABLE 1 – Principaux paramètres à considérer pour le choix d'une diode.

#### 7 Transistors

# 7.1 Qu'est ce qu'un transistor?

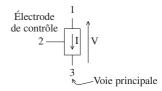

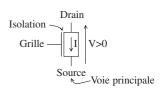

Il en existe plusieurs sortes. Dans tous les cas, ce sont des composants à trois électrodes (trois pattes). Deux des électrodes constituent la voie principale dans lequel le courant peut circuler si on leur applique une différence de potentiel.

La circulation du courant dans la voie principale est contrôlée par le potentiel appliqué ou le courant que l'on fait circuler dans la troisième électrode qui constitue une électrode de pilotage.

Dans tous les cas, le courant dans l'électrode de contrôle est très petit devant le courant qui circule dans la voie principale.

#### 7.2 Utilisation

Les transistors trouvent deux modes d'utilisation : la commutation et les applications linéaires (CF Systèmes linéaires), en particulier l'amplification. Dans le premier, cas le transistor est soit passant soit isolant et fonctionne comme un interrupteur commandé par le signal appliqué sur l'entrée de commande. Dans le deuxième, une tension constante dite de polarisation est appliquée en V. Cette tension peut être assez grande (quelques dizaines de Volts) et correspond potentiellement à un courant relativement grand devant l'entrée de commande. De cette façon, un petit signal (courant ou tension) de commande peut moduler un grand courant dans la voie principale du transistor, créant ainsi la fonction amplification par exemple.

Il existe deux familles de transistors :

- 1. Les transistors à effet de champ : FET (*Field Effect Transistors*). Ce sont ceux utilisés dans les composants logiques donc de fait les plus répandus.

- Dans ces transistors, c'est le champ électrique interne qui est directement responsable du fonctionnement.

- 2. Les transistors bipolaires à jonctions : BJT (Base Junction Transistors). C'est le premier type de transistor

Leur fonctionnement est basé sur des effets de jonction comme pour les diodes.

# 8 Transistors à effet de champ

Parmi les transistors à effet de champ, on distingue les transistors à grille isolée et non isolée. Ce cours ne portera que sur les transistors à grille isolée que sont les MOSFET (*Metal Oxyde Silicium FET*). C'est en effet le composant roi de l'électronique logique.

Il en existe deux types, les transistors à canal N et les transistors à canal P selon le dopage du canal.

# 8.1 MOS canal N (NMOS)

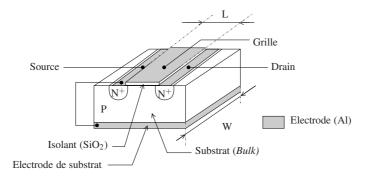

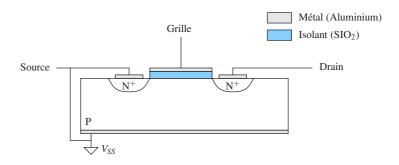

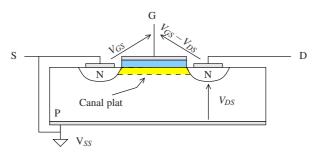

FIGURE 15 – Vue en perspective d'un MOSFET canal N.

Un transistor MOSFET, ou MOS, en abrégé est réalisé comme présenté figure 15. Il est constitué d'un substrat P déposé sur une électrode plane. Cet ensemble constitue le "bulk" ou "body" du transistor (bulk : partie massive en anglais). L'électrode de bulk est en général prise comme référence de potentiel. Au sommet du substrat on réalise deux caissons dopés N, recouverts chacun d'une électrode plane rectangulaire, qui constituent les électrodes de source et de drain. Entre les deux électrodes, on vient déposer une couche d'oxyde de silicium (SiO<sub>2</sub>) isolante. Cette couche isolante est surmontée, elle aussi, d'une électrode rectangulaire de largeur W et de longueur L qui forme l'électrode de grille. Celle-ci est donc isolée du substrat, d'où le nom de transistor à grille isolée. Les grandeurs W et L sont caractéristiques du transistor réalisé et leur rapport W/L détermine certaines de ses propriétés. On brise la symétrie du système en connectant l'électrode de source au potentiel le plus bas ( $V_{SS}$ ). C'est-à-dire à l'électrode de bulk dans la figure 15. Cette connexion permet d'imposer le sens du champ électrique qui sera généré par la polarisation de la grille.

Pour la petite histoire, les noms des électrodes : grille, drain, source sont issus de l'analogie de fonction de ces électrodes avec les composants électroniques à lampes tel que l'Audion de De Forest (1906). La grille est l'électrode de contrôle de ce type de transistor et les électrodes de drain et de source constituent la voie principale. Par définition le courant circule du drain vers la source. C'est cohérent avec la condition imposée :  $V_D > V_S$ , ou  $V_D$  et  $V_E$  sont respectivement les potentiels de Drain et de Source.

intéressante pour donner une idée de la structure d'un MOS. Elle permet, en outre, de définir les dimensions W et L. Elle n'est cependant pas la plus pratique pour en étudier le fonctionnement. Dans la suite on lui préférera une représentation en coupe le long de sa dimension (L) comme ci contre :

Fonctionnement : Si on laisse la grille "en l'air", c'est-à-dire non connectée, entre source et drain on voit une suite de semi-conducteurs NPN c'est-à-dire deux diodes tête-bêches et le courant ne peut pas passer : Source — Drain

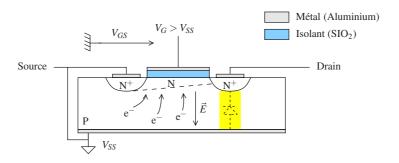

Si on applique un potentiel  $V_G > V_{SS}$  sur la grille, alors on crée un champ électrique entre la grille et le substrat qui attire les électrons, porteurs minoritaires, présents dans le substrat P. Cela crée un canal dopé en électrons, donc N, entre les caissons de source et de drain comme représenté dans la figure ci dessous :

Le courant peut alors passer du drain vers la source, le transistor est passant. Comme le dopage du canal est de type N ce type de transistor est appelé NMOS.

**Remarque :** On notera dans cette situation la présence d'une diode entre drain et substrat. Avec l'électrode de substrat connectée à la masse, cette diode empêche de connecter le transistor à l'envers, c'est-à-dire avec  $V_D < V_s$ .

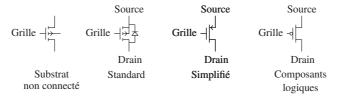

**Symboles :** On trouve de nombreux symboles pour le transistor NMOS dans la littérature et les documentations techniques. Les plus courants sont présentés ci dessous :

Tous les symboles ont en commun de montrer l'isolation de grille : l'électrode de grille n'est pas en contact dans les symboles avec le reste du composant.

Le premier symbole est très général, il représente les trois électrodes grille, drain et source. De plus, la connexion au substrat est représentée comme une électrode additionnelle au milieu. La flèche indique le sens de la diode substrat-canal. De cette façon, on pourra distinguer un MOS canal N d'un MOS canal P que l'on verra plus tard. Ce symbole représente un MOS dont le substrat n'est pas connecté à la source. Il n'est utilisé que dans le cadre de la micro électronique, par les fondeurs de silicium, seuls susceptibles de placer plusieurs MOS côte à côte sur un même substrat.

Le deuxième symbole est le symbole courant des NMOS comme composant unique dans les documentations des fabricants (exemple BS170). Comme il n'y a qu'un seul MOS, le substrat est connecté à la source ce que fait apparaître le symbole. De plus la diode drain substrat est représentée. C'est une information redondante dans le symbole, mais qui peut aider à se souvenir du sens de circulation du courant, cette diode doit être bloquée sinon elle court-circuite le transistor.

Le troisième symbole, est un symbole simplifié très répandu, la flèche indique le sens d'écoulement normal du courant et est placée du côté source. Ce symbole est celui que nous utiliserons en général.

Le dernier symbole est celui souvent utilisé pour les schémas des composants logiques. Drain et source n'y sont pas distingués, mais dans ce contexte la source est nécessairement en bas, et le NMOS est passant pour un niveau haut sur sa grille. Ce symbole se comprend en considérant le symbole du MOS à canal P qui dans le même contexte présente un petit rond sur la grille pour signifier qu'il est passant pour un niveau bas sur sa grille (CF symboles PMOS).

# 8.2 MOS canal P (PMOS)

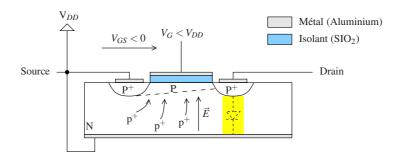

Comme nous l'avons évoqué plus tôt, on peut aussi fabriquer des PMOS :

32

Dans la structure d'un PMOS, la source est cette fois-ci connectée au potentiel le plus élevé  $V_{DD}$ . Les caissons sont dopés P et le substrat N. Avec  $V_{GS} < 0$  cette fois on attire les trous porteurs minoritaires du substrat entre les deux caissons de grille et de drain pour créer un canal P. Dans cette structure, la diode drain substrat est orientée cette fois ci du drain vers la source. En conséquence, dans un PMOS, le courant circule dans le canal de la source vers le drain.

Avec les mêmes principes que pour les symboles du transistor NMOS, les symboles du PMOS sont les suivants :

Dans ces schémas les sources sont placées en haut pour respecter la convention qui consiste à placer les potentiels les plus élevés vers le haut. On peut noter, dans les deux symboles du milieu, le changement de sens de la diode de substrat. Pour le symbole simplifié, la flèche qui indique le sens normal d'écoulement du courant est toujours placée sur la source. On notera que comme, dans un PMOS, le courant circule de la source vers le drain, la flèche pointe cette fois-ci vers le transistor. Le symbole utilisé pour les composants logiques présente comme mentionné plus haut un petit rond sur la grille qui rappel qu'il est passant pour un niveau bas.

Intégration de plusieurs MOS sur un même substrat : Dans les coupes de transistors MOS présentées ci-dessus, la source était toujours connectée au substrat. Ce n'est évidemment pas toujours possible lorsque que l'on intègre plusieurs MOS sur le même substrat et qu'ils sont connectés en série. C'est encore moins possible si l'un des MOS est un NMOS et l'autre un PMOS.

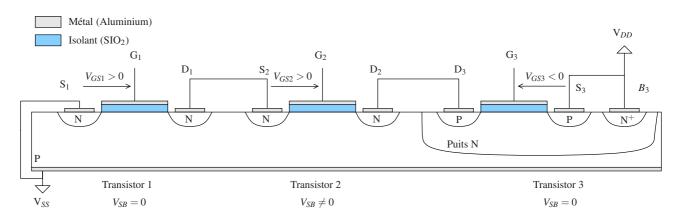

FIGURE 16 – Exemple d'intégration de trois MOSFET canal N et P sur un même substrat.

La figure ci-dessus montre, par exemple, comment il est possible de placer et de connecter en série trois transistors (N, N et P) sur le même substrat. Pour intégrer le transistor PMOS un puits P a été réalisé. Notez l'électrode supplémentaire  $B_3$  qui est l'électrode de substrat du transistor PMOS. Elle permet de connecter au potentiel le plus élevé le substrat du PMOS. On vérifie que le sens possible pour l'écoulement du courant est bien, du drain vers la source, pour les transistors

NMOS et de la source vers le drain pour le PMOS. Enfin, on peut noter que la différence de potentiel grille-source du deuxième transistor n'est pas nulle. Cela influence bien sûr son fonctionnement.

**Applications :** Lorsqu'ils sont utilisés comme composants uniques et discrets, les MOS trouvent la plupart de leurs applications en commutation.

On peut citer les deux références suivantes de transistors MOS à tout faire : BS170 (NMOS), BS250 (PMOS).

En électronique intégrée, le MOS est actuellement le composant roi. C'est le composant de tous les circuits logiques et numériques et des micro-processeurs. Il est aussi à la base des étages d'entrée des amplificateurs opérationnels modernes. En ce qui concerne les applications numériques, la technologie MOS est caractérisée par sa largeur de grille. En 2014, pour l'Intel Core I7 par exemple, elle est de 45 nm pour 10<sup>9</sup> transistors intégrés.

### 8.3 Caractéristiques statiques des transistors NMOS, modèle de Schichman et Hodges

En fonction de la tension appliquée sur la grille, le transistor est soit bloqué, soit passant si l'on a créé un canal. Ce modèle simpliste est suffisant pour expliquer ce qu'est un transistor et pour en comprendre le fonctionnement, mais il ne permet pas de calculer la valeur des composants qui vont entourer le MOS dans un circuit. Si le MOS est passant, qu'elle est sa résistance? C'est une des premières questions que l'on peut se poser. La physique précise d'un transistor MOS est complexe, mais bien connue. Elle est hors du champ de ce cours et dans celui de physique du solide. Nous en utiliserons les résultats nécessaires sans les démontrer.

#### 8.3.1 Courant de grille

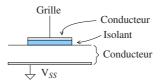

Vue de la grille, un MOS est un condensateur dont la valeur dépend de W et L et de l'épaisseur de l'isolant ( $S_1O_2$ ):

L'oxyde de silicium est un très bon isolant. On peut considérer pour la caractéristique statique (à fréquence nulle) que le courant de grille est nul :

$$I_G = 0 (15)$$

L'ordre de grandeur de la résistance de fuite est en effet de l'ordre de grandeur de quelque TeraOhm  $(10^{12}\,\Omega)$ .

#### 8.3.2 Courant drain-source

Dans un premier temps, nous nous plaçons dans l'hypothèse  $V_{SB} = 0$  pour établir la caractéristique du NMOS. Nous verrons comment la valeur de la tension source-substrat la modifie par la suite.

**Transistor Bloqué :** Comme nous l'avons vu dans la section précédente, on cherche à emmener des électrons porteurs minoritaires entre la source et la grille pour créer un canal de conduction. Ces électrons ne bougent pas librement dans un substrat P. Le canal ne peut se créer qu'à partir d'une certaine valeur de la tension  $V_{GS}$  que l'on appelle tension de seuil :  $V_T$ . Il est bloqué tant que :

$$V_{GS} < V_T$$

(16)

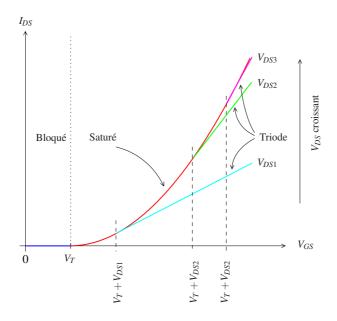

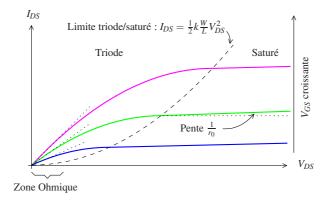

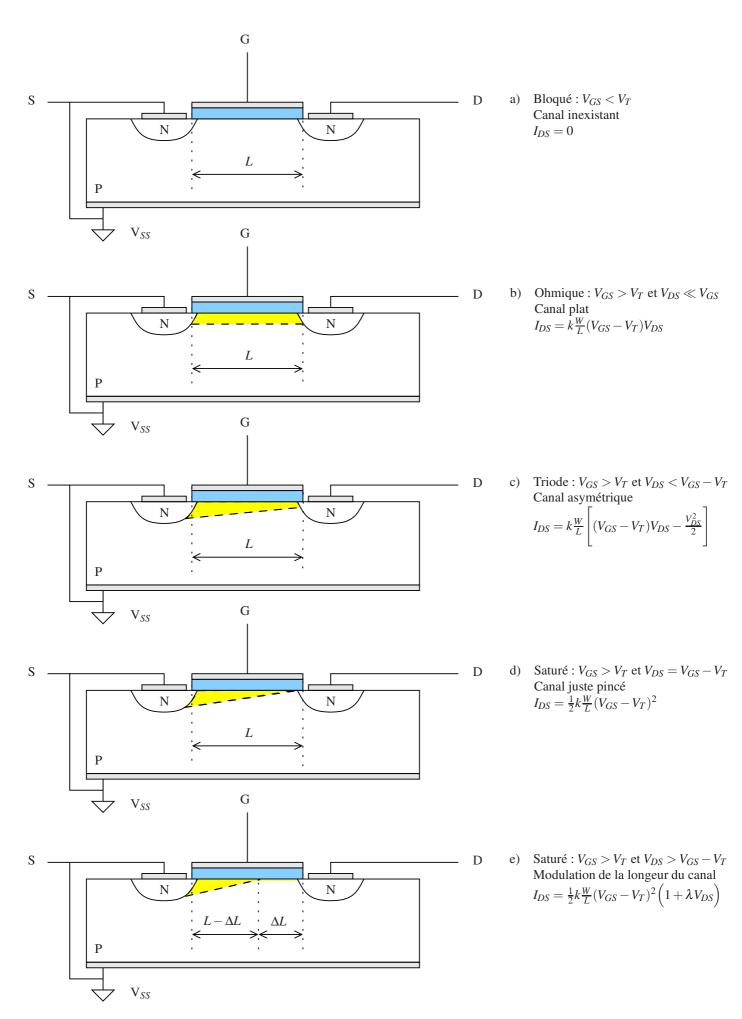

Le courant de drain est donc nul quelque soit la tension appliquée entre le drain et la source (zone bloquée figure 17).

FIGURE 17 – Caractéristique NMOS :  $I_{DS}$  en fonction de  $V_{GS}$ .

**Transistor passant :**  $V_{GS}$  est maintenant supérieure à la tension de seuil, le canal existe. Il est alors possible d'appliquer une différence de potentiel  $V_{DS}$  pour y faire circuler du courant.

#### Mode Ohmique:

Si  $V_{DS}$  est suffisamment petite pour que  $V_{GS} \approx V_{GS} - V_{DS}$  (c'est-à-dire  $V_{GS} \approx V_{GD}$ ) alors le champ électrique qui règne dans la structure est homogène et le canal est plat, comme représenté ci-dessous.

L'épaisseur ep du canal est proportionnelle à  $V_{GS}-V_T$  :  $ep=\alpha(V_{GS}-V_T)$ , où  $\alpha$  dépend de la mobilité des porteurs. Le courant  $I_{DS}$  circule donc dans une zone de longueur L et de section  $S=\alpha(V_{GS}-V_T)W$  contenant des porteurs libres. Il se comporte donc comme une résistance de valeur  $R=\rho L/S$ , où  $\rho$  est la conductivité du canal. On en déduit avec la loi d'Ohm le courant drain-source :  $\frac{\alpha}{\rho}\frac{W}{L}(V_{GS}-V_T)V_{DS}$ . En posant  $k=\frac{\alpha}{\rho}$ , que l'on appelle le facteur de gain du transistor, on obtient :

Courant mode Ohmique

$$I_{DS} = k \frac{W}{T} (V_{GS} - V_T) V_{DS}$$

(17)

En remarquant que la condition  $V_{GS} \approx V_{GS} - V_{DS}$  peut s'exprimer comme  $V_{DS} \ll V_{GS}$ , c'est-à-dire  $V_{DS}$  petit, on se trouve dans la zone ohmique de la caractéristique  $I_{DS} = f(V_{GS})$  présentée figure 18.

k est généralement exprimé en  $\mu$ A/V<sup>2</sup>. On peut montrer que :

$$k = \mu_{e^-}.C_{\text{ox}} \tag{18}$$

Dans cette équation  $\mu_{e^-}$  est la mobilité des électrons et  $C_{\rm ox}=\frac{\mathcal{E}_{\rm ox}}{d_{\rm ox}}$  la capacité par unité de surface de la grille.  $d_{\rm ox}$

FIGURE 18 – Caractéristique NMOS :  $I_{DS}$  en fonction de  $V_{DS}$ .

est l'épaisseur de la couche isolante d'oxyde de Silicium et  $\varepsilon_{ox}$  sa permittivité (condensateur plan  $C = \varepsilon \frac{S}{d}$ ). Le lecteur vérifiera qu'avec la définition de la mobilité :  $\vec{v}_{(m/s)} = \mu \vec{E}$ , k est bien homogène à des Ampères par Volts carrés.

#### Mode Triode:

$V_{DS}$  augmente. La condition  $V_{GS} \approx V_{GD}$  n'est plus respectée. Le canal n'est plus symétrique (figure 19-c), il est plus épais du côté de la source où la différence de potentielle  $V_{GS}$  est plus grande que du côté du drain  $V_{GD} = V_{GS} - V_{DS}$ . Elle correspond en effet à un champ électrique plus intense. Le canal se pince (figure 19-d), c'est-à-dire que son épaisseur devient nulle lorsque  $V_{GD}$  devient égale à la tension de seuil :  $V_{GD} = V_{GS} - V_{DS} = V_T$ . On reste en régime triode tant que  $V_{GD} > V_T$  soit tant que  $V_{GS} - V_{DS} > V_T$ . Finalement, on est en régime triode tant que :  $V_{DS} < V_{GS} - V_T$ .

Le modèle de Shichman et Hodges (S-H) donne le courant de drain pour le mode triode :

Mode triode

$$V_{DS} \le V_{GS} - V_T \tag{19}$$

$$I_{DS} = k \frac{W}{L} \left[ (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(20)

**Remarque :** Lorsque  $V_{DS}$  est suffisamment petite,  $V_{DS}^2 \ll (V_{GS} - V_T)V_{DS}$  et l'on retrouve l'expression du courant de mode Ohmique. Le mode Ohmique est un cas particulier du mode triode.

La figure 18, présente les modes ohmique et triode ainsi que la courbe qui sépare le mode triode du mode saturé qui suit. Cette courbe correspond à la limite  $V_{DS} = V_{GS} - V_T$ . L'équation de cette courbe s'obtient en remplaçant  $(V_{GS} - V_T)$  par  $V_{DS}$  dans l'équation 20 :

Limite du mode triode

$$I_{DS} = \frac{1}{2} k \frac{W}{L} V_{DS}^2 \tag{21}$$

#### Mode saturé, modulation de la longueur de canal, effet Early :

Lorsque le canal est juste pincé, le courant n'est contrôlé que par la zone de pincement. Le courant transistor est dit saturé car  $I_{DS}$  est alors quasi indépendant de  $V_{DS}$ . Il est donné par le modèle de S-H :

Courant de saturation

$$I_{DS} = I_{\text{sat}} = \frac{1}{2} k \frac{W}{L} (V_{GS} - V_T)^2$$

(22)

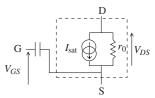

$I_{\rm sat}$  ne dépend pas de  $V_{DS}$ . Le transistor se comporte comme une source de courant commandée par  $V_{GS}$ .

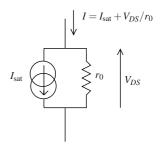

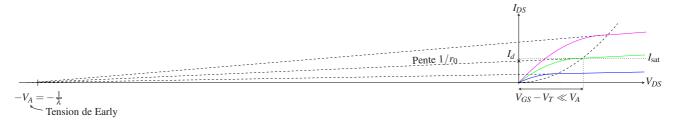

Bien sur, une source de courant idéale n'existe pas et  $I_{DS}$  dépend légèrement de  $V_{DS}$  comme présenté sur la courbe du milieu de la figure 18. Cet effet est simplement modélisable par une grande résistance en parallèle avec un générateur de courant fournissant  $I_{\text{sat}}$ . Cette résistance est en fait la résistance interne du générateur.

Cet effet vient de la variation de la longueur du canal avec l'augmentation de  $V_{DS}$  comme présenté figure 19-e.

En effet, le canal existe car  $V_{GS} > V_T$  et le courant est contrôlé par la zone de pincement. La zone pincée s'étend avec  $V_{DS}$ , ce qui se traduit par une légère augmentation du courant de saturation, qui est modélisable par une résistance en parallèle. Ce n'est là qu'un modèle de comportement. Le phénomène exact n'est pas simple.

Si l'on prolonge les droites correspondant aux zones saturées dans la caractéristique  $I_{DS} = f(V_{DS})$  pour différentes valeurs de  $V_{GS}$  comme dans la figure ci-dessus, on constate qu'elles passent toutes par le point  $(-V_A, 0)$ .  $V_A$  est appelé tension de Early. Elle est proportionnelle à L la longueur du canal.  $\lambda = \frac{1}{V_A}$  est appelé coefficient de modulation de la longueur du canal.

La résistance  $r_o$  dépend de  $V_{GS}$ :  $r_0 = \frac{\partial I_{DS}}{\partial V_{DS}}|_{V_{GS}=\mathrm{cste}} = \frac{V_A}{I_d} = \frac{1}{\lambda I_d}$ . Comme la valeur de  $r_0$  est très grande,  $I_d \approx I_{\mathrm{sat}}$  soit  $r_o \approx \frac{1}{\lambda I_{\mathrm{sat}}}$ . Avec la même hypothèse on peut négliger  $(V_{GS}-V_T)\frac{1}{r_0}$  devant  $(I_{\mathrm{sat}}-I_d)$ , on écrit :  $I_{DS}=I_{\mathrm{sat}}+\frac{V_{DS}}{r_0}$ . Finalement, on modélise l'effet de la variation de la longueur du canal par l'équation 23

Modèlisation de l'effet Early

$$I_{DS} = \frac{1}{2} k \frac{W}{L} (V_{GS} - V_T)^2 (1 + \lambda V_{DS})$$

(23)

Dans la plupart des cas, cet effet est négligeable ( $r_0$  très grande) et on n'en tiendra en général pas compte. En pratique on n'en tient compte que si on arrive à un résultat incohérent ou impossible sans en tenir compte.

## ON UTILISE TOUJOURS LE MODÈLE LE PLUS SIMPLE POSSIBLE

#### 8.4 Validité du modèle

Le modèle présenté est valable au premier ordre, il est donc relativement grossier. Il permet cependant les raisonnements et les calculs à la main à  $\pm 10\%$  près. Lorsqu'une précision supérieure est nécessaire, ce qui n'est en général pas le cas pour l'électronique de tous les jours, il faut avoir recours aux logiciels de simulation.

#### 8.4.1 Paramètres d'influences

**Effet de substrat :** Dans ce qui précède, le potentiel du substrat est supposé être le même que celui de la source :  $V_{SB} = 0$ . Or cela n'est parfois pas le cas, comme pour le transistor du milieu de la figure 16. Dans ce cas le fonctionnement du NMOS est légèrement modifié. Il ne s'agit cependant que d'un ajout au modèle précédent, ce dernier reste vrai. Le modèle corrigé est peu utile en pratique, et ne sera pas présenté ici.

FIGURE 19 – Résumé du fonctionnement d'un transistor NMOS.

Effets de la température : Deux effets sont ici en compétition.

- 1.  $\frac{\partial V_T}{\partial T} < 0$ , la température aide à "décrocher" les porteurs minoritaires de réseau cristallin, ce qui fait augmenter  $I_{DS}$

- 2.  $\frac{\partial k}{\partial T} < 0$ , la température augmente la résistivité du canal ce qui a tendance à diminuer  $I_{DS}$ . Cet effet est prépondérant.

Finalement,  $I_{DS}$  diminue avec la température

## 8.5 Stratégies de calcul : schémas équivalents

Comme pour les diodes, il n'est pas toujours facile lorsque que l'on se trouve devant un circuit comprenant un transistor, de trouver le bon angle d'attaque. La bonne méthode consiste toujours à déterminer dans quel mode (Bloqué, Ohmique,..., ou saturé) se trouve le MOS. Pour les transistors MOS, cela se fait en déterminant  $V_{GS}$  puis, si  $V_{GS} > V_T$ , en comparant  $V_{GS}$  à  $V_{DS} - V_T$ . Ensuite, on remplacera le transistor par le schéma équivalent correspondant à son état. Pour un transistor  $V_{GS}$  saturé, on le remplace par le schéma ci-contre, qui fait apparaître un générateur de courant qui correspond au courant de saturation.

Le schéma équivalent doit faire apparaitre toutes les électrodes d'entrée du MOS. Dans ce schéma le condensateur modélise la capacité grille-source.  $I_{DS}$  ne dépend pour un MOS saturé que de  $V_{GS}$ . La capacité grille-source dépend de la surface de l'électrode de grille  $W \times L$ . Elle est responsable des performances en terme de vitesse du transistor. Il faut en effet la charger ou la décharger pour modifier  $V_{GS}$ . L'amélioration des performances des MOS est actuellement liée à la diminution conjointe de la surface de l'électrode de grille et de la tension d'alimentation  $V_{DD}$ , ce qui permet de diminuer la quantité de charge nécessaire à la polarisation de la grille (CF table 2). Pour un NMOS en régime Ohmique, le schéma équivalent, serait celui d'une résistance pilotée par la valeur de  $V_{GS}$ . A l'aide du schéma équivalent, on peut commencer à "raisonner électronique", c'est-à-dire à utiliser les lois d'Ohm, des nœuds , des mailles, et le théorème de superposition.

| Année | W                    | $V_{DD}$  |

|-------|----------------------|-----------|

| 1974  | 3 μm                 | 5 V       |

| 1995  | 0.35 μm              | 3.3 V     |

| 1999  | $0.18  \mu \text{m}$ | 1.8 V     |

| 2007  | 65 nm                | 1.2-0.8 V |

TABLE 2 – Évolution des tailles de gravures et tension d'alimentation en technologie MOS

## 8.6 Caractéristique statique des transistors PMOS.

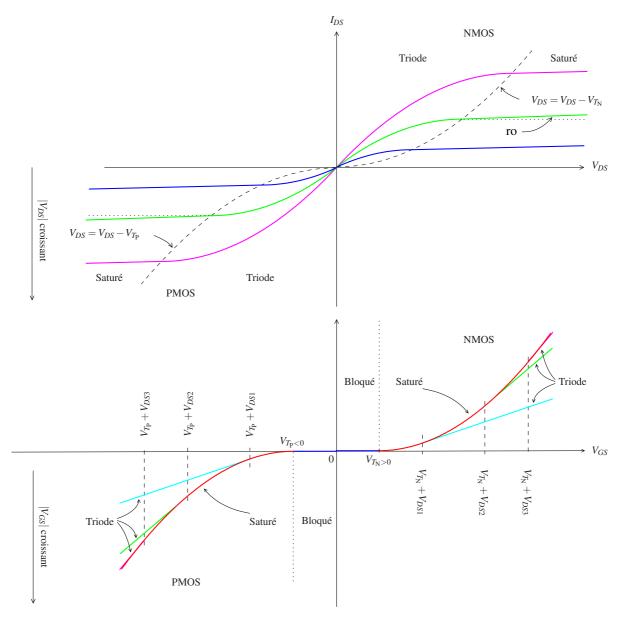

Les transistor PMOS se comportent de la même façon que les NMOS au signe des tensions près ( $V_{GS} < 0$  et  $V_{DS} < 0$ ) et au sens du courant ( $I_{DS} < 0$ ) puisqu'il circule de la source vers la grille comme présenté section 8.2. Pour créer le canal, il faut  $V_{GS} < V_T$  avec  $V_T < 0$ . Un fois le canal créé, si l'on augmente  $|V_{DS}|$  le canal est successivement plat, juste pincé, pincé avec modulation de la longueur. Le transistor est alors successivement en mode ohmique, triode, puis saturé comme le NMOS. Les équations du modèle de S-H permettent, là encore, de quantifier le courant. La figure 20 résume, en le comparant au NMOS, le fonctionnement des transistors PMOS. Notons que en général  $|V_{T_P}| \neq |V_{T_N}|$ . Ceci n'apparait pas dans la figure 20 pour des raisons de clarté .

FIGURE 20 – Comparaisons des caractéristiques PMOS et NMOS.

## 8.6.1 Mises en œuvre comparées des transistors NMOS et PMOS.

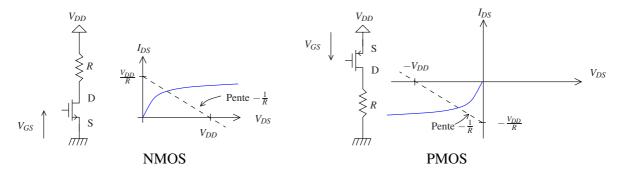

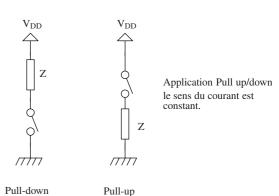

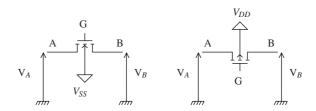

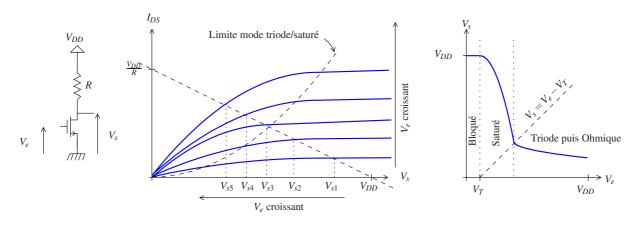

Le fonctionnement des NMOS est contrôlé par la tension  $V_{GS}$  avec  $V_G > V_S$ , alors que pour les PMOS  $V_G < V_S$ . Ils doivent donc être mis en œuvre de telle sorte que ces conditions soient respectées. Cela se fait typiquement de la façon suivante :

la tension  $V_{GS}$  peut ainsi être directement imposée aux transistors pour contrôler leurs blocages respectifs. Notez que

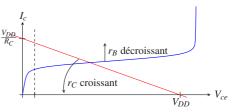

R permet d'amener le transistor en mode ohmique, triode ou saturé, en fonction de sa valeur, en imposant la tension  $V_{DS}$  pour une tension  $V_{GS}$  donnée, comme le montrent les droites de charge.

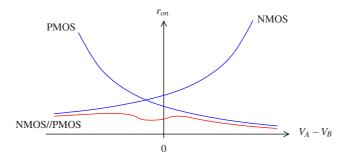

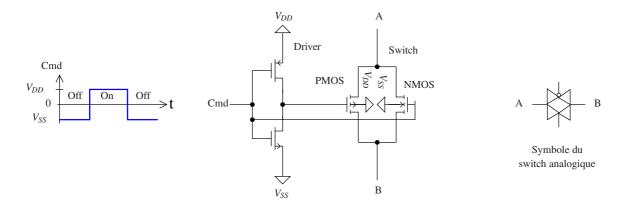

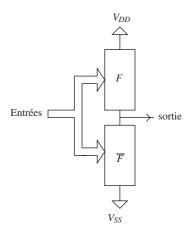

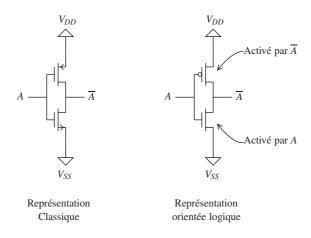

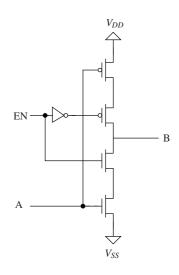

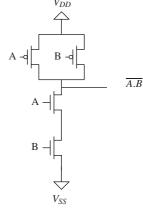

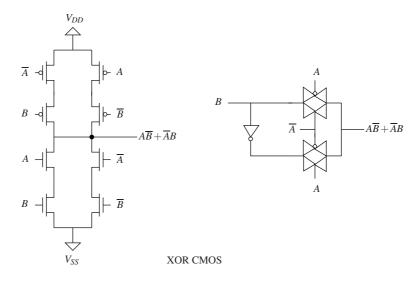

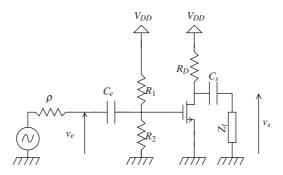

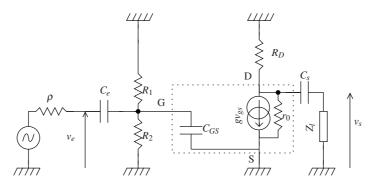

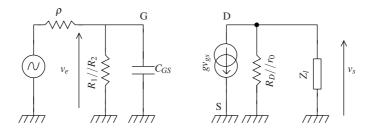

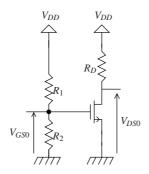

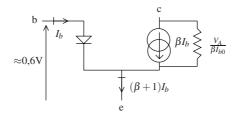

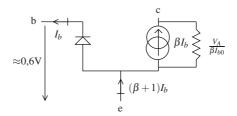

## 8.7 Transistors MOS à apauvrissement